# High Performance Scientific Computing Using FPGAs for Lattice QCD

# **Owen Callanan**

A thesis submitted to the University of Dublin, Trinity College in fulfilment of the requirements for the degree of Doctor of Philosophy (Computer Science)

October 2006

# **Declaration**

| I, the undersigned, declare that this work has not been previously submitted to  | this or |

|----------------------------------------------------------------------------------|---------|

| any other University, and that unless otherwise stated, it is entirely my own wo | ork.    |

\_\_\_\_

Owen Callanan

Dated: 31 October 2006

# Permission to Lend and/or Copy

| I, the undersigned, agree that Trinity College Library may lend or copy this thesis |  |

|-------------------------------------------------------------------------------------|--|

| upon request.                                                                       |  |

|                                                                                     |  |

|                                                                                     |  |

|                                                                                     |  |

|                                                                                     |  |

|                                                                                     |  |

| Owen Callanan                                                                       |  |

Dated: 31 October 2006

# **Summary**

The recent development of large FPGAs combined with the availability of a variety of FPGA-based non-integer arithmetic cores has made it possible to implement high-performance matrix kernel operations on FPGAs. This thesis seeks to evaluate the performance of FPGAs for real scientific computations by implementing lattice Quantum Chromodynamics (lattice QCD), which is one of the classic scientific computing problems. Lattice QCD computing machinery is the focus of considerable research work worldwide, including two custom ASIC based solutions and a variety of custom built PC cluster machines. This wide variety of highly optimised lattice QCD computing machinery permits comparison with the state of the art for high performance computing machinery.

The results presented in this thesis give significant insights into the usefulness of FPGAs for scientific computing. This thesis also evaluates two different number systems available for running scientific computing applications on FPGAs. FPGA based lattice QCD processors are implemented using both double precision IEEE floating point and logarithmic arithmetic cores with precision equivalent to IEEE single precision floating point. The performance of the FPGA based lattice QCD processors is compared with that of two lattice QCD targeted custom ASIC based supercomputers, with that of commercial supercomputers and with that of some highly optimised PC cluster based machines.

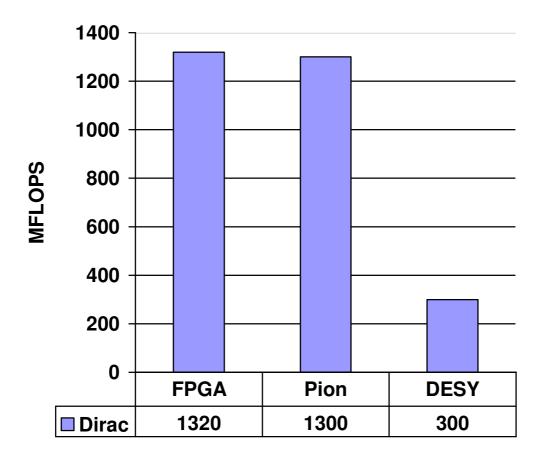

The logarithmic arithmetic designs return per FPGA performance of 1320 MFLOPS for the performance critical lattice QCD Dirac operator, and they return 1050 MFLOPS for the full conjugate gradient solver application. The latest generation of PC clusters return per processor performance of about 1300 MFLOPS for the Dirac operator using single precision arithmetic. Thus the logarithmic arithmetic designs are competitive with the latest PC cluster machines, which are the main platform for single precision lattice QCD calculations.

The double precision designs return performance of 1200 MFLOPS for the core

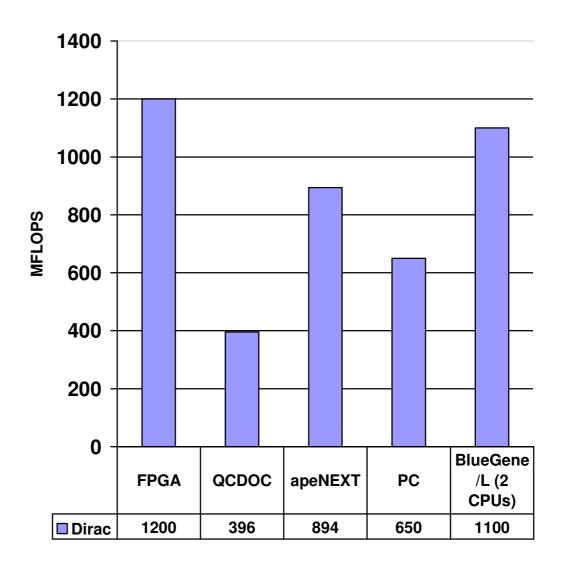

Dirac operator and 940 MFLOPS for the conjugate gradient solver application. This compares very well with the double-precision per-processor performance of the latest PC clusters at 650 MFLOPS and with the performance of the IBM BlueGene/L supercomputer at 1100 MFLOPS per processor. BlueGene/L processors consist of an ASIC with two CPU cores, so the per-core performance of the BlueGene/L is 550 MFLOPS. The double precision FPGA design's performance also compares very well with the per-processor performance of the two custom ASIC supercomputers that have been constructed specifically for lattice QCD. The QCDOC machine has per-processor performance of 396 MFLOPS, whilst the apeNEXT system has per-processor performance of 894 MFLOPS. All figures are for the Dirac operator.

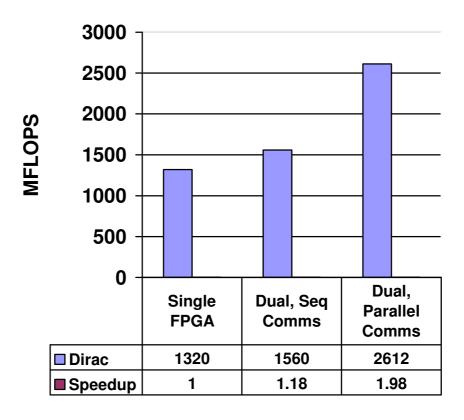

All current lattice QCD machines are constructed using many processors. The computational requirements of lattice QCD are so great that they can never be met by a single processor. To investigate the viability of multiple-FPGA based systems, a dual FPGA version of the Dirac operator was implemented. Lattice QCD is a highly parallelisable problem and can be implemented efficiently on multiple processor machines. The dual-FPGA Dirac operator, which is based on the logarithmic Dirac operator, uses a low latency communications system to allow two FPGAs to work together on a single application of the Dirac operator. A speedup of 1.98 times is delivered over the single FPGA design, by parallelising computation and calculation in the dual FPGA design. This result strongly indicates that FPGAs have the potential to form a scalable multiple processor platform for high performance computing applications such as lattice QCD.

These three sets of results demonstrate that FPGAs can return excellent performance for a typical high performance computing application, lattice QCD, using two different arithmetic systems. Double precision floating point is the most commonly used arithmetic system for high performance computing applications. This makes the results from the double precision designs particularly significant since they demonstrate that FPGAs can return highly competitive performance for real scientific computing applications using double precision arithmetic. Finally the dual-FPGA Dirac operator demonstrates that FPGAs have the potential to form a scalable

multiple processor platform for high performance computing.

# Acknowledgements

Many people helped me complete this thesis, but no one did more than my supervisor David Gregg. His advice and guidance was vital to the completion of this work, and for this I owe him many thanks.

I would also like to thank Mike Peardon and Jim Sexton for their invaluable expert advice and information on lattice QCD and for providing the algorithms that provided the basis of this work. Thanks are also due to my initial supervisor, Andy Nisbet, for seeing me through the first 2 years of my PhD.

I shared an office with several people over the last four years, and, along the way, they helped me in many ways with my research. I would like to thank Emre Ozër for helping me greatly in my initial efforts at publication, and also Milan Tichy for giving me the benefit of his considerable FPGA design expertise and knowledge. Their assistance was invaluable. I would also like to thank Ross Brennan and Eoin Creedon for many interesting discussions and for helping me solve many tricky problems.

I could not have started this work without the support of my parents and family, and I certainly would never have finished it. Their support and patience helped my through many obstacles and kept me going through difficult times. Simple thanks are not enough, but they will have to suffice (at least for now).

Finally, above all, thanks to Eadaoin Boyle-Tobin, for everything.

# **Contents**

| List of Figu | res                                         | xxii |  |

|--------------|---------------------------------------------|------|--|

| List of Tabl | es                                          | xxvi |  |

| Chapter 1    | Introduction                                | 1    |  |

| 1.1 FP       | PGAs for Scientific Computing               | 2    |  |

| 1.2 La       | ttice QCD & Lattice QCD Machines            | 3    |  |

| 1.3 Ar       | rithmetic Systems                           | 4    |  |

| 1.4 Co       | ontributions                                | 4    |  |

| 1.5 Pu       | blications Related to this Thesis           | 5    |  |

| 1.6 Gu       | nide to this Thesis                         | 6    |  |

| Chapter 2    | Technologies                                | 11   |  |

| 2.1 FP       | PGAs                                        | 11   |  |

| 2.1.1        | The Alpha Data ADM-XRC II Prototyping Board | 14   |  |

| 2.1.2        | ADM-XRC-II Board Support Package            | 15   |  |

| 2.2 Ha       | ardware design languages                    | 17   |  |

| 2.2.1        | Handel-C                                    | 18   |  |

| 2.2.2        | Basic use of Handel-C                       | 19   |  |

| 2.2.3        | Data Storage in Handel-C                    | 21   |  |

| 2.3 Nu       | umber Representations                       | 22   |  |

| 2.3.1        | Single Precision Log and Floating Point     | 22   |  |

| 2.3.2     | Double Precision IEEE Floating Point                              | 25 |

|-----------|-------------------------------------------------------------------|----|

| 2.4 Sun   | nmary                                                             | 28 |

| Chapter 3 | Literature Survey                                                 | 29 |

| 3.1 QC    | D and Lattice QCD                                                 | 30 |

| 3.1.1     | Quantum Chromodynamics                                            | 30 |

| 3.1.2     | Lattice QCD                                                       | 32 |

| 3.1.3     | Lattice QCD Dirac operator                                        | 35 |

| 3.1.4     | The conjugate gradient method                                     | 35 |

| 3.1.5     | Conjugate gradient in lattice QCD                                 | 36 |

| 3.1.6     | Operations and data for the lattice QCD conjugate gradient solver | 38 |

| 3.2 Latt  | tice QCD Computing Machines                                       | 40 |

| 3.2.1     | Commercial Supercomputers                                         | 41 |

| 3.2.2     | PC Clusters                                                       | 43 |

| 3.2.3     | Custom ASIC based machines – QCDOC & apeNEXT                      | 45 |

| 3.3 IEE   | E Floating Point                                                  | 50 |

| 3.3.1     | Early History                                                     | 50 |

| 3.3.2     | The IEEE Floating Point Standard                                  | 51 |

| 3.3.3     | Early Implementations of Floating point on FPGAs                  | 52 |

| 3.3.4     | Current State of the Art for Floating Point on FPGAs              | 54 |

| 3.3.5     | The Future of Floating Point on FPGAs                             | 60 |

| 3.4 Lo    | ogarithmic Arithmetic                              | 65 |

|-----------|----------------------------------------------------|----|

| 3.4.1     | Early investigations of logarithmic number systems | 65 |

| 3.4.2     | Towards a hardware implementation                  | 66 |

| 3.4.3     | Hardware Implementations of Logarithmic Arithmetic | 68 |

| 3.4.4     | HSLA Multiplication and Division                   | 70 |

| 3.4.5     | Addition and Subtraction                           | 71 |

| 3.4.6     | Accuracy and Performance of the HSLA System        | 72 |

| 3.4.7     | Comparing LNS and IEEE floating point              | 72 |

| 3.5 Su    | ımmary                                             | 73 |

| Chapter 4 | Algorithm Analysis                                 | 75 |

| 4.1 Pe    | erformance Metrics and Considerations              | 75 |

| 4.2 Cl    | ock Rate and Path Delay                            | 76 |

| 4.3 Ex    | xploiting Low Level Parallelism                    | 78 |

| 4.4 Aı    | nalysis Techniques                                 | 79 |

| 4.5 Aı    | nalysis Results                                    | 79 |

| 4.6 Pa    | rallelism in the Dirac operator                    | 81 |

| 4.7 Pa    | rallelism in the Dot Product Operator              | 82 |

| 4.8 Pa    | rallelism in the Matrix Add-Scale Operator         | 83 |

| 4.9 Su    | nmary                                              | 84 |

| Chapter 5 | Lattice QCD Using Logarithmic Arithmetic           | 85 |

| 5.1 Log   | g arithmetic Dirac operator implementation                   | 85  |

|-----------|--------------------------------------------------------------|-----|

| 5.1.1     | LNS arithmetic unit analysis                                 | 86  |

| 5.1.2     | LNS arithmetic use in the Dirac operator                     | 87  |

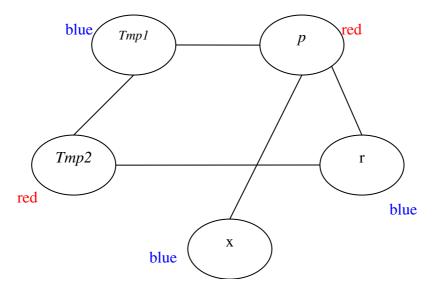

| 5.1.3     | Gamma-Mul Block Design                                       | 88  |

| 5.1.4     | Matrix Addition, Matrix Subtraction and Matrix Scale Designs | 91  |

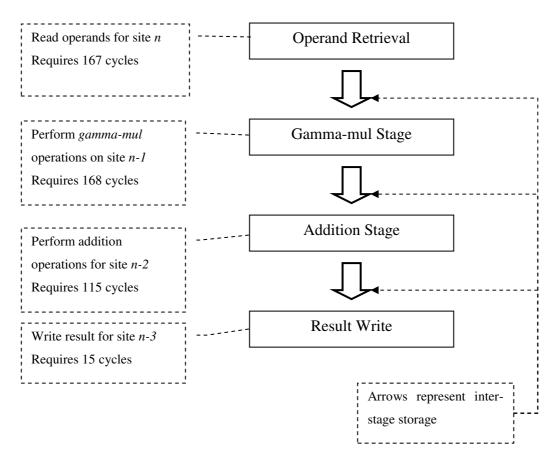

| 5.1.5     | Dirac Operator Pipeline                                      | 92  |

| 5.2 Log   | g arithmetic conjugate gradient solver                       | 96  |

| 5.2.1     | LNS Matrix Add-Scale and Dot Product operators               | 96  |

| 5.2.2     | Memory Layout                                                | 97  |

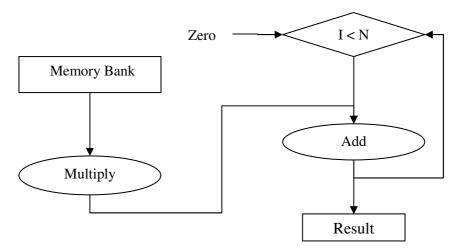

| 5.2.3     | Log arithmetic dot product operator                          | 99  |

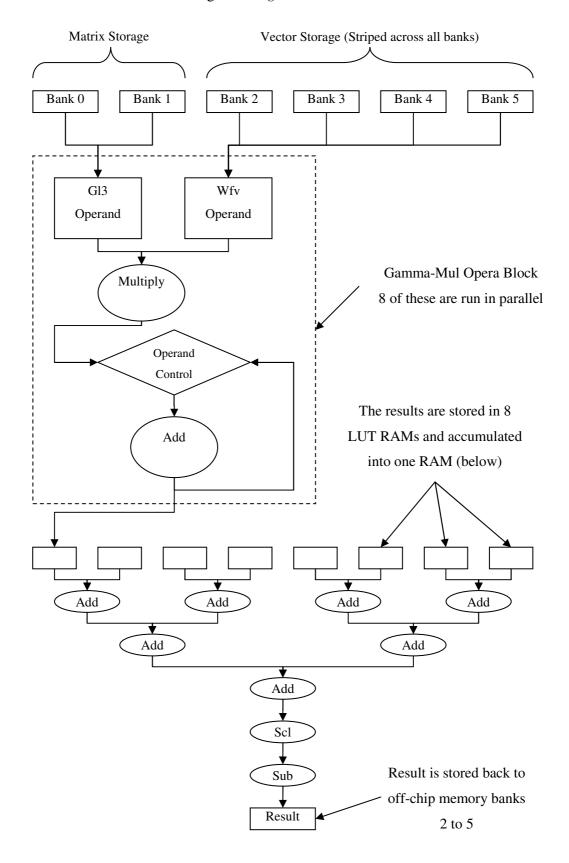

| 5.2.4     | Log arithmetic matrix add-scale operator                     | 100 |

| 5.3 Sur   | nmary                                                        | 101 |

| Chapter 6 | Lattice QCD Using IEEE Double Precision Arithmetic           | 103 |

| 6.1 Des   | sign Constraints for Double Precision Arithmetic             | 104 |

| 6.2 Doi   | uble precision IEEE arithmetic unit analysis                 | 105 |

| 6.3 Doi   | uble precision Dirac operator implementation                 | 106 |

| 6.3.1     | Use of On-Chip Block RAM memory                              | 107 |

| 6.3.2     | The gamma-mul pipeline stage                                 | 108 |

| 6.3.3     | Addition stage                                               | 111 |

| 6.3.4     | Data storage and layout                                      | 114 |

| 6.3.5   | Resource utilisation reduction                    | 115 |

|---------|---------------------------------------------------|-----|

| 6.4     | Double precision conjugate gradient solver        | 116 |

| 6.4.    | Double precision matrix add-scale operator        | 116 |

| 6.4.2   | 2 Double precision dot-product operator           | 116 |

| 6.5     | Summary                                           | 117 |

| Chapter | 7 Dual FPGA Dirac Operator                        | 119 |

| 7.1     | Partitioning the Dirac operator algorithm         | 119 |

| 7.2     | Communications requirements of the Dirac operator | 120 |

| 7.3     | Hardware Infrastructure                           | 122 |

| 7.4     | Existing Inter-FPGA Communications Systems        | 122 |

| 7.5     | Source Synchronous Communications                 | 124 |

| 7.6     | Implementing the design                           | 126 |

| 7.6.    | FIFO queues and Handel-C                          | 126 |

| 7.7     | Communications protocol                           | 129 |

| 7.8     | Communication difficulties                        | 131 |

| 7.8.    | Errors in the communication system                | 131 |

| 7.8.2   | 2 Solving the communication problems              | 132 |

| 7.9     | Summary                                           | 134 |

| Chapter | 8 Results                                         | 135 |

| 8 1     | Correctness testing                               | 135 |

| 8.2     | Performance measurement methodology                           | 136 |

|---------|---------------------------------------------------------------|-----|

| 8.3     | Log arithmetic implementation results                         |     |

| 8.4     | Double precision implementation results                       | 141 |

| 8.4.    | 1 Effect of problem size on double precision FPGA performance | 145 |

| 8.5     | Dual FPGA implementation results                              | 146 |

| 8.5.    | 1 Measuring performance for the dual FPGA Dirac operator      | 146 |

| 8.5.    | 2 Performance Results                                         | 147 |

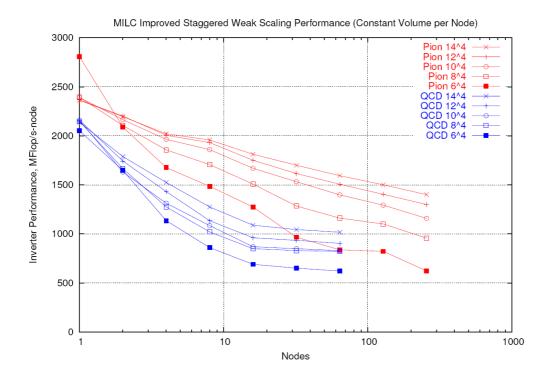

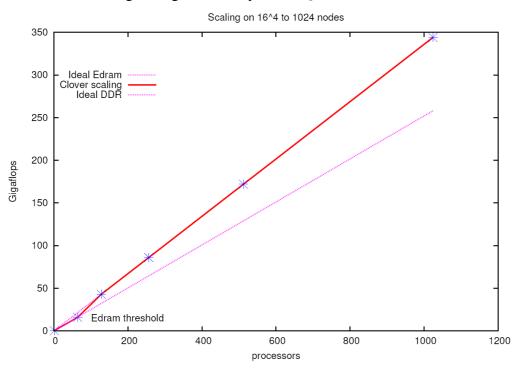

| 8.5.    | 3 Scalability Comparisons                                     | 148 |

| 8.6     | Notes on comparing performance of lattice QCD machines        | 151 |

| 8.7     | Summary                                                       | 153 |

| Chapter | 9 Final Thoughts                                              | 155 |

| 9.1     | The Suitability of FPGAs for High Performance Computing       | 155 |

| 9.2     | Contributions of this Thesis                                  | 156 |

| 9.3     | Limitations of This Work and Suggestions for Future Work      | 158 |

| 9.4     | Conclusion                                                    | 160 |

| Append  | ix A Pipelined Use of Arithmetic Units                        | A-1 |

| A.1     | Gamma Functions                                               | A-1 |

| A.2     | Multiply Functions                                            | A-4 |

| A.3     | Combining Gamma and Multiply Functions                        | A-8 |

| Append  | ix B Clock Rate Improvement Example                           | B-1 |

| R 1     | Sources of Delay                                              | R-1 |

| B.2    | Delay in the Dirac Pipeline Control Structure     | B-2      |

|--------|---------------------------------------------------|----------|

| B.3    | Pipelining the SITE Calculation                   | B-4      |

| B.4    | Modulus Operator Elimination                      | B-5      |

| B.5    | Changing to DK3                                   | B-6      |

| B.6    | Final Clock Rate Optimisation                     | B-7      |

| Append | ix C Conjugate Gradient Operator Source Code      | C-1      |

| C.1    | Main.c                                            | C-3      |

| C.2    | Latops.c                                          | C-5      |

| C.3    | Ops.c                                             | C-9      |

| C.4    | Gamma.c                                           | C-16     |

| C.5    | Ran.c                                             | C-27     |

| C.6    | Qcddefs.h                                         | C-38     |

| C.7    | Qcdtypes.h                                        | C-39     |

| Append | ix D Handel-C code for double precision conjugate | gradient |

| implem | entation                                          | D-1      |

| D.1    | Main.hcc                                          | D-3      |

| D.2    | Gamma.hcc                                         | D-11     |

| D.3    | CG_ops.hcc                                        | D-41     |

| D.4    | SRAM_functions.hcc                                | D-53     |

| D.5    | Types.hch                                         | D-80     |

| D.6    | Variables.hch                                     | D-82     |

| Appendix E | Layout on FPGA of double precision Dirac operator | E-1 |

|------------|---------------------------------------------------|-----|

| References |                                                   | I   |

# **List of Figures**

| Figure 2-a. Logical diagram of the ADM-XRC-II development board showing the            |

|----------------------------------------------------------------------------------------|

| connection of the Virtex-II FPGA to the PCI bus, off-ship SRAM memory and other        |

| off-chip components [Alpha-Data '05]                                                   |

| Figure 2-b. The ADC-PMC carrier card used in this work, with a single ADM-XRC-         |

| II development card fitted                                                             |

| Figure 2-c. Use of Handel-C par{} block to specify parallelism                         |

| Figure 2-d. A complex expression causing a low clock rate                              |

| Figure 2-e. Pipelined and parallelized Handel-C loop                                   |

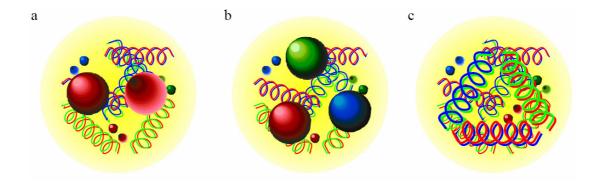

| Figure 3-a. The three types of hadrons that can exist in nature; Mesons, Baryons and   |

| Glueballs [Davies '00]                                                                 |

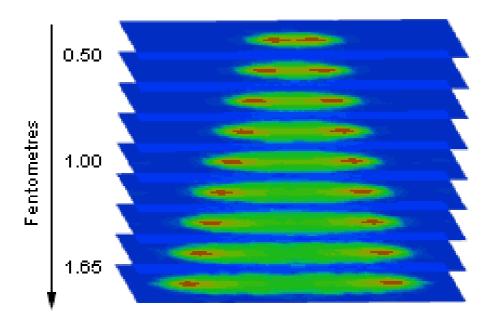

| Figure 3-b. A lattice calculation showing how the strength of force develops as you    |

| pull a quark and an anti-quark apart, which prevents them escaping from one another    |

| [Davies '03]                                                                           |

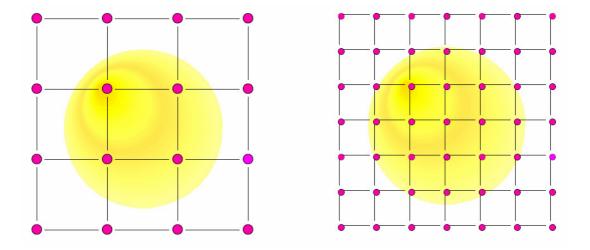

| Figure 3-c. Diagram showing how a lattice is used to simulate space and time around    |

| a hadron. The lattice must be larger than the hadron in all dimensions. A lattice with |

| more points (the lattice on the right) will give a more accurate result but will take  |

| more computer time to simulate                                                         |

| Figure 3-d. Main loop of lattice QCD conjugate gradient solver                         |

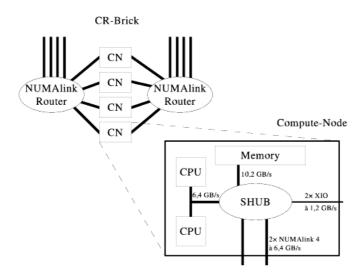

| Figure 3-e. SGI Altix Architecture [Wettig '05]                                        |

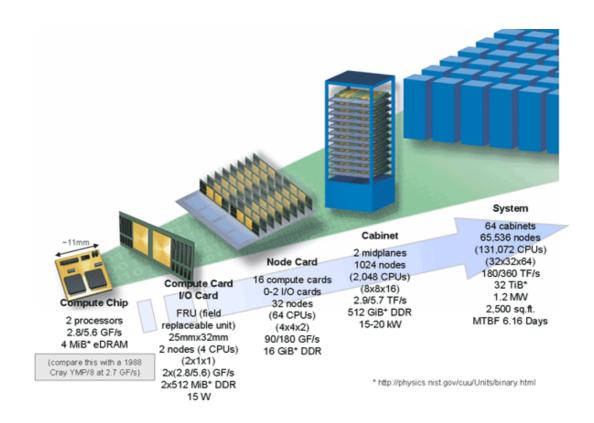

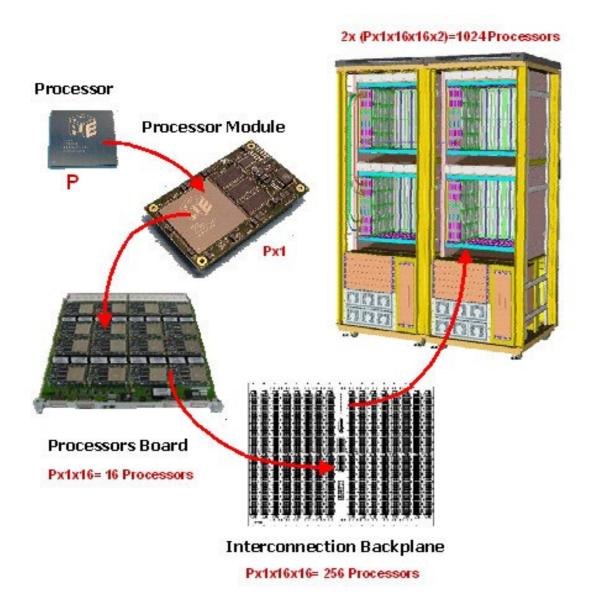

| Figure 3-f. The construction of a large BlueGene/L supercomputer                       |

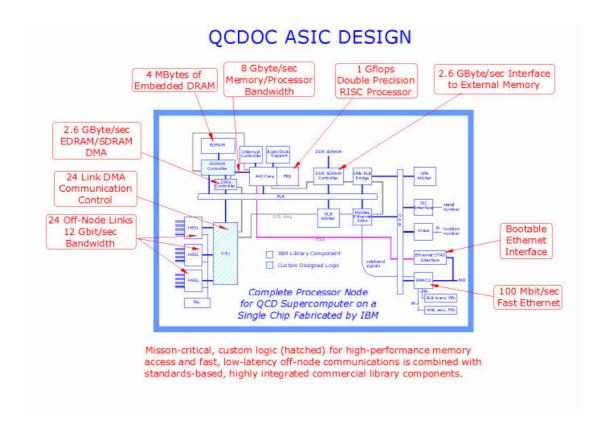

| Figure 3-g. The design of a single QCDOC processor                                     |

| Figure 3-h. The structure of a large aneNEXT machine.                                  |

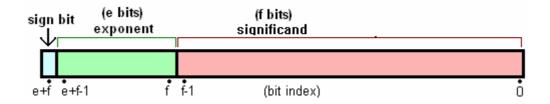

| Figure 3-i. Structure of the IEEE floating point word                                                                                                                                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

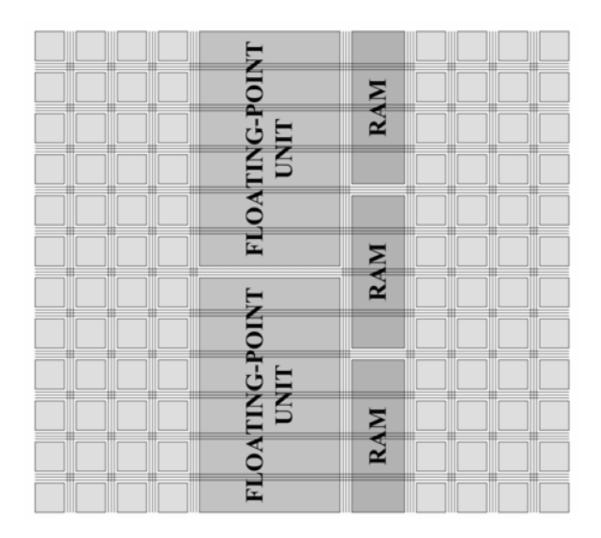

| Figure 3-j. A diagram of the embedded floating point FPGA architecture proposed by Beauchamp et al [Beauchamp '06a]                                                                                                    |

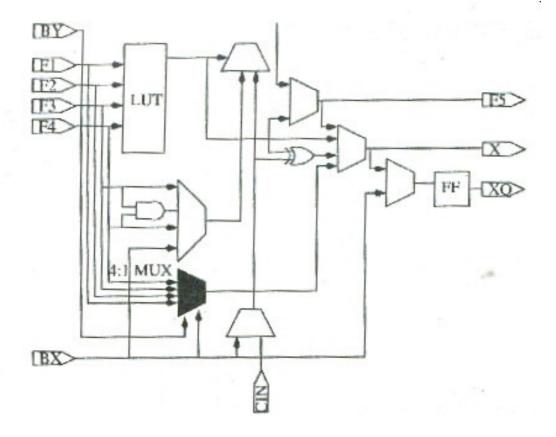

| Figure 3-k. A diagram of the new CLB structure proposed by Beachamp et al [Beauchamp '06b]. A 4:1 MUX has been added to the CLB to improve performance of the variable shifters required for floating point arithmetic |

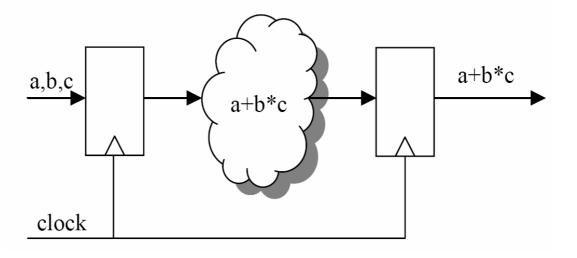

| Figure 4-a. An example of an un-pipelined circuit with a large logic delay77                                                                                                                                           |

| Figure 4-b Pipelined version of the circuit shown in Figure 4-a                                                                                                                                                        |

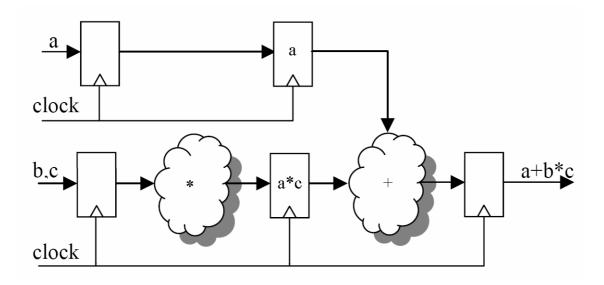

| Figure 5-a. Source code for a complex number matrix multiply routine. This code, combined with a gamma operation makes up a <i>gamma-mul</i> block                                                                     |

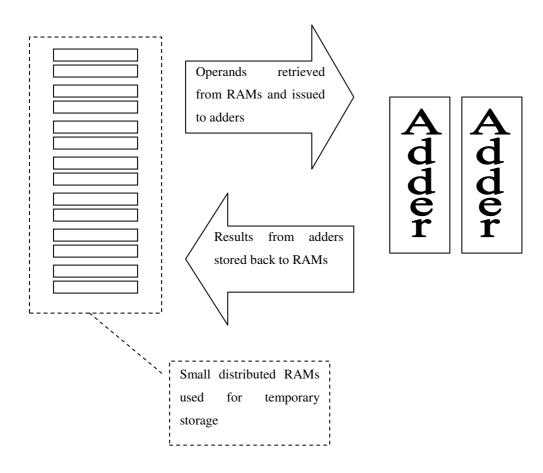

| Figure 5-c. Operand issue and result retrieval function used to implement matrix addition in the Dirac operator pipeline                                                                                               |

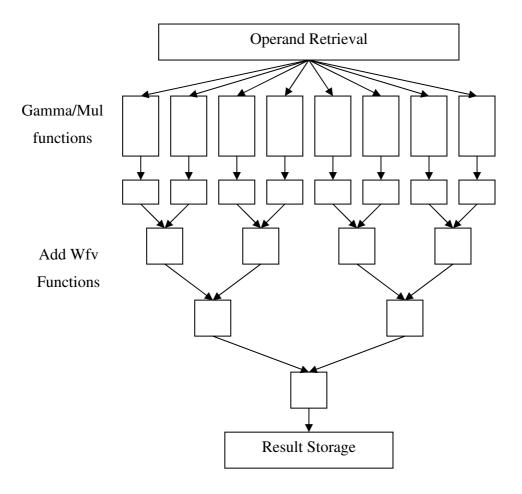

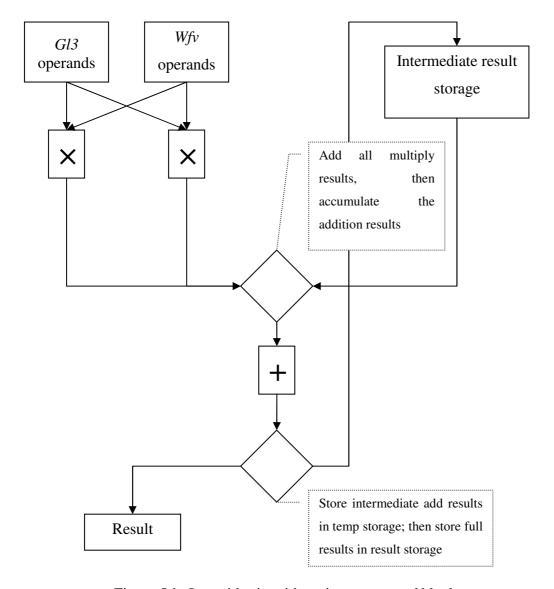

| Figure 6-a. The architecture of the double precision Dirac operator. A diagram of the design of the <i>gamma-mul</i> blocks is inset                                                                                   |

| Figure 8-a. Performance of log arithmetic FPGA design and comparable systems 140                                                                                                                                       |

| Figure 8-b. Performance of double precision Dirac operator and comparable systems                                                                                                                                      |

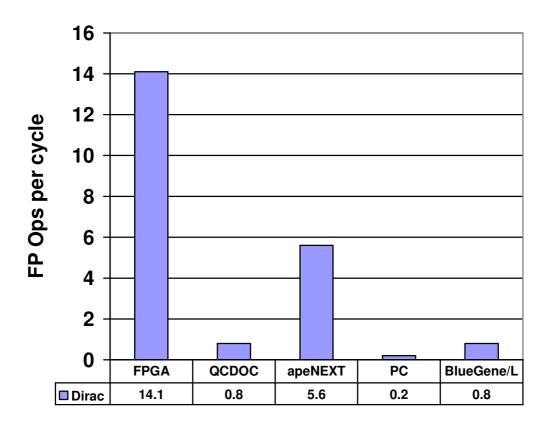

| Figure 8-c. Floating Point operations performed per cycle by various lattice QCD systems                                                                                                                               |

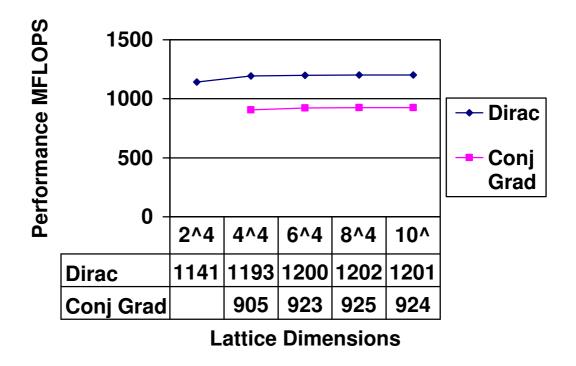

| Figure 8-d. Effect on performance of increasing problem size for the double precision FPGA designs. Performance is constant for problem sizes larger than 6 <sup>4</sup> .                                             |

| Figure 8-e. Performance of single & dual FPGA Dirac operators                                                                                                                                                          |

| Figure 8-f. Scaling properties of lattice QCD targeted PC clusters. Performance is for                                                                                                                                 |

| single precision arithmetic. Reproduced from [Holmgren '06]14                          | 18 |

|----------------------------------------------------------------------------------------|----|

| Figure 8-g. Scalability of the QCDOC machine                                           | 50 |

| Figure 9-a. Layout of FPGA when programmed with the double precision Dira              | ac |

| operator design from Chapter 6. Each of the blocks of colour is one of the arithmet    | ic |

| units, the light green colour is the general application logic. Any grey areas represe | nt |

| logic that is not used in the design.                                                  | -2 |

# **List of Tables**

| Table 2-a. Comparison of the resource requirements of two log arithmetic adder                                                |

|-------------------------------------------------------------------------------------------------------------------------------|

| pipelines and a comparable IEEE floating point adder pipeline23                                                               |

| Table 2-b. Comparison of the log arithmetic multiplier and a comparable IEEE floating point multiplier                        |

| Table 2-c. Comparison of the resource requirements of the log arithmetic divider and a comparable IEEE floating point divider |

| Table 2-d. Comparison of double precision adders                                                                              |

| Table 2-e. Comparison of double precision multipliers27                                                                       |

| Table 2-f. Comparison of selected dividers                                                                                    |

| Table 3-a. Area in silicon of three FPGA components. One unit is the area required for a single FPGA slice                    |

| Table 4-a. Arithmetic operations per site for lattice QCD operations79                                                        |

| Table 4-b. Memory characteristics and arithmetic operation distribution for lattice QCD operations                            |

| Table 5-a. Memory bandwidth requirements per site update for Dirac operator94                                                 |

| Table 8-a. Floating point operations per site for the lattice QCD operators                                                   |

| Table 8-b. Performance of the log arithmetic designs                                                                          |

# Chapter 1

# Introduction

Scientific computing has an insatiable appetite for processing power. For several decades computers have been used to investigate natural phenomena such as fluid dynamics, particle simulations and even the weather. By simulating these phenomena using computer simulations we can gain a greater understanding of how the underlying systems work, and predict the future behaviour of these systems.

The use of computers in science is not restricted to simulating the known behaviour of natural phenomena. A significant branch of scientific computing has developed where computer simulations are used to test mathematically expressed scientific theories that are too complex to be proven by solving the equations of the theory, and which cannot be proven by experimental observation.

This technique is used heavily in a particular branch of sub-atomic particle physics theory called quantum chromodynamics, or QCD. QCD theory attempts to explain the behaviour of sub-atomic particles called quarks, which are the basic components of particles like protons and neutrons. However quarks can never actually be observed on their own as they are always bound together inside a larger particle. This makes QCD theory impossible to verify through experimental observation alone.

As a result, physicists have turned to using computer simulations to simulate their theories about how quarks behave. By comparing the results of these simulations to the results obtained from experiments conducted using large particle colliders, such as those at CERN and Fermilab, physicists can test QCD theory. This use of

computer simulations to test QCD theory is commonly referred to as lattice QCD.

The computational requirements of these lattice QCD simulations are very large. The latest generation of dedicated lattice QCD computing machines have sustained performance for a single problem of several Teraflops (10<sup>12</sup> floating point operations per second). With these machines physicists are able to test QCD theory more rigorously than ever before. Yet even these machines are not enough; the lattice QCD community is already discussing how to build Petaflop (10<sup>15</sup> floating point operations per second) scale machines.

Lattice QCD is only just one of many scientific computing applications which have huge computational requirements, but it provides an excellent example application for testing the performance of a new computing platform for scientific computing. In common with many scientific computing applications, it is matrix based, and is highly parallelisable. Also a significant amount of research effort has been spent on developing dedicated lattice QCD computing machinery, including two custom-ASIC based supercomputers [Belletti '06][P A. Boyle '05]. Commercial supercomputers and PC clusters are also used extensively for lattice QCD. These lattice QCD machines represent the state of the art of scientific computing machinery.

# 1.1 FPGAs for Scientific Computing

FPGAs, or field programmable gate arrays, are dynamically reprogrammable microchips that can be programmed to take on the behaviour of any digital circuit. They can be used to implement processors that are customised to the specific needs of an application, without the prohibitive expense and design complexity of producing a custom application specific integrated circuit (ASIC). FPGA based processors have been used successfully for some time for integer and fixed-point arithmetic domain applications such as digital signal processing. Designers are able to exploit the inherent parallelism available on an FPGA to implement processors that return excellent performance for these applications.

Historically FPGAs have not been large enough to support a significant number of

floating arithmetic units on a single FPGA, which has limited the use of FPGAs for scientific computing. However recent multi-million gate equivalent FPGAs make it possible to implement complex, high-performance designs incorporating floating point arithmetic. Investigating the use of FPGAs for high performance scientific computing is now a significant branch of reconfigurable computing research [Underwood '04b][Zhuo '04].

This thesis investigates the performance of FPGAs for *full* floating-point based scientific applications by implementing the lattice QCD Dirac operator, which is the performance critical part of nearly all lattice QCD simulations. The operator is used to implement a full lattice QCD conjugate gradient solver. The performance results of these implementations are compared with the performance of a number of platforms currently used for lattice QCD simulations.

# 1.2 Lattice QCD & Lattice QCD Machines

Improving the performance of lattice QCD is the focus of considerable research work worldwide [Wettig '05], including two competing custom ASIC supercomputers targeted solely at lattice QCD simulations [Belletti '06][P A. Boyle '05]. Several groups are also investigating optimizing PC clusters for lattice QCD, [Gellrich '03][Holmgren '05a][Holmgren '05b][Holmgren '06]. Lattice QCD has also been implemented on the latest generation of commercial supercomputers including the IBM BlueGene/L and the SGI Altix machines [Wettig '05]. This considerable body of research allows a comparison of the performance of the FPGA based solution with the state of the art for scientific computing.

The core of lattice QCD is the *Dirac operator*, a large complex floating-point intensive matrix computation. Although the performance of the Dirac operator is central, lattice QCD involves other operations which can have a significant impact on performance. The impact of these operations is investigated by implementing a full example application, a lattice QCD conjugate gradient solver which uses the Dirac operator.

The computational requirements of lattice QCD are too great to be met by a single

processor. Machines used for lattice QCD consist of many processors connected together to work on the same problem. For example one QCDOC machine, an example of the custom ASIC supercomputers mentioned previously, consists of 12,288 interconnected custom ASIC processors, which can all work together on the same problem. Such a machine can sustain over five teraflops (10<sup>12</sup> floating point operations per second) on actual lattice QCD simulations. Consequently a single FPGA will never be sufficient to meet the demands of a full lattice QCD simulation. I have implemented a dual-FPGA version of the core Dirac operator to investigate whether multiple FPGA based systems are good for lattice QCD.

# 1.3 Arithmetic Systems

This thesis also aims to compare the suitability of different non-integer arithmetic systems for high performance computing applications on FPGAs. A comparison of logarithmic arithmetic and IEEE double precision floating point is presented. This comparison is used to identify the strengths and weaknesses of both arithmetic systems when used for real high performance scientific computing applications. Logarithmic arithmetic is very different to conventional IEEE floating point, and thus has very different constraints when used for real applications.

Performance results are presented for both log arithmetic and IEEE double precision arithmetic versions of the full conjugate gradient solver along with results for the component parts of the conjugate gradient application. These results include performance data for the performance critical Dirac operation. A quantitative comparison is also presented with three categories of lattice QCD systems: ASIC-based processors designed exclusively for lattice QCD, highly optimised PC cluster systems and finally commercial supercomputers. Finally results are presented for a dual-FPGA Dirac operator. These results show that parallelisation of calculation and inter-FPGA communication can maximise performance for multiple-FPGA systems.

### 1.4 Contributions

This thesis evaluates the viability of FPGAs for real scientific computing applications by implementing FPGA designs that are customised to the needs of a

specific, highly demanding, application, lattice QCD.

## • Performance of FPGAs for Scientific Computing

The performance of FPGAs is evaluated for a typical, full scientific computing application, lattice QCD. Lattice QCD computing machinery is the focus of a substantial amount of research effort worldwide. By comparing the results obtained from the work described in this thesis with this body of research I am able to give significant insights into the performance of FPGAs for scientific computing.

## • Arithmetic Systems for FPGAs

In this thesis performance critical lattice QCD algorithms are implemented for both single precision equivalent logarithmic arithmetic and IEEE compliant double precision floating point. The results of these implementations show the advantages and disadvantages of each arithmetic system when applied to scientific computing applications. Also the double precision implementations are amongst the first FPGA-based implementations of double precision scientific computing applications whilst the logarithmic arithmetic designs are the first successful use of log arithmetic for scientific computing.

## • Multiple FPGA processing for scientific computing

The final stage of this work implements a dual FPGA version of the performance critical Dirac operator. This work demonstrates that two FPGAs can work together on the same problem, and can return excellent performance. The result shows that FPGAs have the potential to be used as the basis for highly parallel scientific computing machines that consist of multiple FPGAs.

### 1.5 Publications Related to this Thesis

The work presented in this thesis has been published in IEEE sponsored international

conferences. The implementation of the logarithmic arithmetic Dirac operator, described in Chapter 5, was previously presented at the 12<sup>th</sup> Reconfigurable Architectures Workshop, which was held as part of the 19<sup>th</sup> IEEE International Symposium on Parallel and Distributed Processing in 2005 [Callanan '05]. The work described in this paper is the authors own work. The other authors contributed to the paper in the following ways: Jim Sexton provided the original lattice QCD algorithm along with information and expertise on lattice QCD, Emre Ozër aided the work at the design stages and played a significant role in writing the final paper, whilst Andy Nisbet and David Gregg both supervised my PhD studies. Andy Nisbet was my original supervisor when this work commenced, however after Andy Nisbet left his position in Trinity College, David Gregg took over as supervisor.

The double precision Dirac operator and conjugate gradient solvers detailed in Chapter 6 were presented at the IEEE sponsored 16<sup>th</sup> International Conference on Field Programmable Logic and Applications in 2006 [Callanan '06]. The logarithmic arithmetic conjugate gradient solver, along with an improved version of the logarithmic arithmetic Dirac operator, was also presented at this conference. The work described in this paper is the authors own. The contributions of the credited authors are as follows: Mike Peardon provided the conjugate gradient application along with lattice QCD expertise, and once again David Gregg and Andy Nisbet are credited for their roles in supervising the PhD work.

## 1.6 Guide to this Thesis

## **Chapter 2**

This chapter presents background information on the systems and technologies used in the work. This information is presented to aid understanding of the work performed for this thesis. An overview of FPGA technology is presented, together with a description of the FPGA development boards used to implement the designs I created for this thesis. Also presented are details of the two arithmetic systems used, logarithmic arithmetic and IEEE floating point arithmetic.

### Chapter 3

A comprehensive review of the literature is contained in this chapter, starting with a discussion of what quantum chromodynamics (QCD) theory attempts to explain and why computer simulations must be used to test this theory. The application of computer simulations to test QCD theory is called lattice QCD. A number of articles, written for a general audience by QCD experts, are used to help with this explanation.

A survey of the state of the art of lattice QCD machinery is then presented. Three categories of machine are used for lattice QCD simulations; custom ASIC based supercomputers, commercial supercomputers and PC clusters. All three categories are discussed in detail.

The chapter concludes with a detailed history of the two arithmetic systems used in this work, combined with a review of recent FPGA research into both systems. The first system reviewed is IEEE double precision floating point arithmetic. The history of floating point arithmetic is presented together with a description of the IEEE floating point standard. The development of FPGA based floating point arithmetic is then presented, up to the most recent investigations of common scientific computing kernels for FPGAs using double precision arithmetic.

The second arithmetic system reviewed is logarithmic arithmetic, which is used as an alternative arithmetic system in this work. The concept of logarithmic arithmetic has existed for some time; however it is only now with the availability of FPGA implementations of the system that it is viable for use on real applications. The history of the logarithmic arithmetic system is described, up to the latest FPGA implementation of the logarithmic arithmetic system that is used in this work.

## Chapter 4

A detailed algorithm analysis is the subject of this chapter. The analysis is presented separately since it is relevant to all three implementation chapters that follow. The core lattice QCD Dirac operator is analysed in detail, opportunities for parallelisation are identified, and the memory bandwidth requirements of the operator are described. The analysis is then repeated for the conjugate gradient solver application, and for

the extra operations that it requires. This analysis formed a vital input to the designs presented in the next three chapters.

## Chapter 5

The design and implementation of the first of the three main components of this thesis is discussed in this chapter. This part of the work consists of an FPGA based Dirac operator implementation which uses logarithmic arithmetic for all non-integer arithmetic. This work was then used to produce a full lattice QCD conjugate gradient solver on an FPGA. These implementations are the first use of logarithmic arithmetic on FPGAs for high performance computing problems. Consequently the performance of these designs offers significant insight into the suitability of FPGA based logarithmic arithmetic for scientific computing.

## Chapter 6

The initial stage of this work, detailed in Chapter 5 used logarithmic arithmetic to handle all non-integer arithmetic. Logarithmic arithmetic was partly chosen because of the limited availability of conventional IEEE floating point arithmetic cores at the start of the project. However during the project double precision floating point cores became available for FPGAs. Users of lattice QCD prefer double precision arithmetic since it gives a more accurate result, however single precision arithmetic can be used, with some algorithmic adjustments to compensate for the lower precision.

Double precision is the standard arithmetic system for scientific computing, single precision does not have sufficient range or precision for many scientific computing applications. Thus the results of an investigation of double precision floating point are applicable to the full range of scientific computing applications. To investigate the performance of double precision floating point arithmetic on FPGAs, double precision versions of the lattice QCD algorithms were implemented.

The designs detailed in this chapter provide important insights into the performance of double precision floating point arithmetic on FPGAs when used for complete applications. The prior work on double precision floating point arithmetic on FPGAs has been primarily concerned with matrix kernel operations, and there has been little work on full applications.

#### Chapter 7

Lattice QCD calculations have massive computational requirements which cannot be met by single processor machines. However lattice QCD simulations are highly parallelisable and can be run successfully on massively parallel machines. All machines currently used for lattice QCD simulations are highly parallel multiple processor machines, which can use many processors on a single calculation. It is highly unlikely that a single FPGA lattice QCD machine will ever have sufficient computational power for full lattice QCD simulations.

This chapter details the design and implementation of a bi-directional FPGA communication system, and its use to implement a dual FPGA version of the logarithmic arithmetic Dirac operator that was presented in Chapter 5. This dual FPGA Dirac operator has nearly twice the performance of the single FPGA version. The performance critical Dirac operator takes up over 90% of the time in lattice QCD simulations and requires only nearest neighbour communications when implemented on multiple processor machines. Consequently the results for this part of the work demonstrated that FPGAs have the potential to be a scalable platform for lattice QCD simulations

#### **Chapter 8**

This chapter presents performance results for the three parts of this work and compares these results with the performance of each of the three categories of machines that are used for lattice QCD simulations, which are described in Chapter 3. Much research effort is devoted to developing computing machinery for lattice QCD simulations and, as a result, these machines can be taken to represent the state of the art for scientific computing machinery. By comparing the performance of my FPGA based designs with these systems I am able to offer significant insights into

the performance of FPGAs for scientific computing applications.

## Chapter 9

In the last chapter a number of issues raised by the results presented in this thesis are discussed, and the thesis concludes with a summary of the contributions of my work, and together with an outline of some interesting areas for future work.

# Chapter 2

# **Technologies**

This chapter presents background information on the technologies and tools that were used to complete this work. A brief overview of FPGAs and the specific architectural features of the FPGAs used in this work are presented. This is followed by a description of the FPGA development platforms used to implement the designs in hardware. The designs in this thesis were implemented using Handel-C which is a hardware design language that offers a higher level of abstraction than existing FPGA design tools such as VHDL or Verilog. The development and history of Handel-C is discussed, along with its advantages over more conventional hardware design tools. Some basic examples of Handel-C code are included to show how Handel-C is used for FPGA design. Finally the two packages of non-integer arithmetic cores that are used are discussed, and they are compared with examples of equivalent floating point units that are taken from the literature.

#### 2.1 FPGAs

FPGA stands for field programmable gate array. FPGAs are a category of programmable logic devices, or PLDs, that can be programmed in the field (hence the name) after manufacture. The devices themselves consist of an array of logic cells which can be programmed and connected together to implement complex digital circuits in hardware. There are a number of different types of logic cell on current FPGAs. They are:

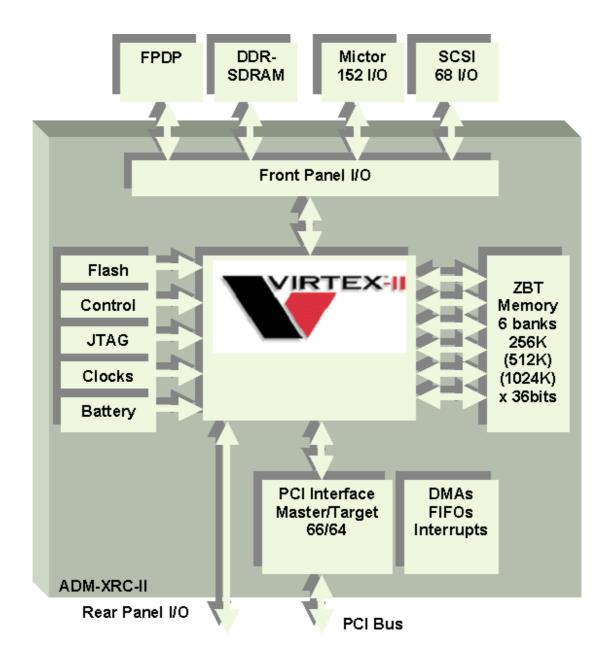

Figure 2-a. Logical diagram of the ADM-XRC-II development board showing the connection of the Virtex-II FPGA to the PCI bus, off-ship SRAM memory and other off-chip components [Alpha-Data '05]

- Slices (containing two flip flops and two small look up tables)

- Block RAMs

- Hardware Multipliers

- IO Blocks

Slices are the most basic type of logic cell and are the foundation of FPGA technology. The flip-flops in a slice are used to implement register storage and the look-up tables are mainly used to implement logic, such as multipliers, adders or shifters. On recent generations of FPGAs the small look up tables can also be used to construct small on-chip RAMs called distributed RAMs. These distributed RAMs are an efficient storage mechanism for small arrays of data in an FPGA based design.

Recent FPGAs, such as the Xilinx Virtex-II used in this thesis, include two other types of logic cell; 18×18 bit hardware multipliers, and dual-ported RAMs, called block RAMs. Integer multipliers consume a lot of FPGA resources when constructed using conventional slices. The hardware multipliers provide a more efficient way to multiply integers on-chip. The block RAM cells are small 18 kilobit RAMs that are available for on-chip storage of data, and they substantially improve the data storage capacity of modern FPGAs. Sophisticated Input/Output blocks are the final type of logic cells. These cells connect the pins of the FPGA chip to the FPGA logic, and They support many different IO standards allowing FPGAs to communicate with many different devices.

FPGAs allow system designers to get the benefits of customising their processor architecture to the needs of their application, without the significant cost and risk of producing their own custom application specific integrated circuit (ASIC) chip. The non-recoverable engineering costs associated with a designing and producing a new ASIC chip grow with each new generation of silicon technology. The non-recoverable engineering cost for the latest 65nm silicon fabrication technology is now in the order of millions of dollars. For a chip using this technology to be commercially successful the manufacturer must sell a very significant number. So for small volume production custom ASIC chips are getting less and less attractive. Meanwhile these improvements in process technologies are making FPGAs larger, faster, cheaper and more capable than ever. Consequently FPGAs are becoming more and more attractive for a wide variety of fields where a custom ASIC processor would be technically beneficial but not financially viable. One such area is high performance computing.

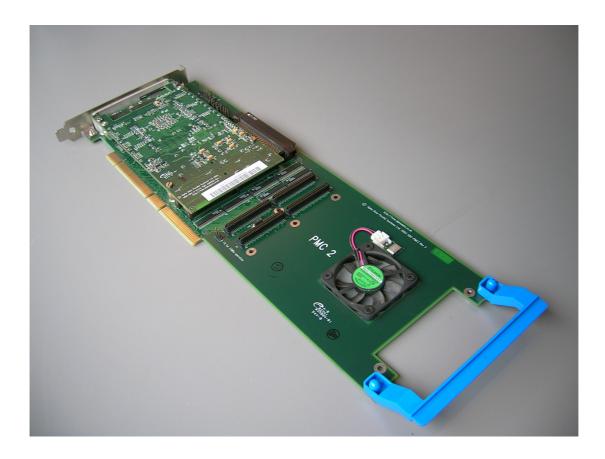

Figure 2-b. The ADC-PMC carrier card used in this work, with a single ADM-XRC-II development card fitted.

FPGAs give system designers access to significant levels of fine-grain instruction level parallelism and this parallelism has long been used to improve performance for application areas such as digital signal processing (DSP). FPGAs have been widely used to accelerate integer and fixed-point domain applications for some time. However, due to the significant device resources required by floating point arithmetic units, FPGAs have previously been too small to use for floating point calculations. FPGAs are now available that are large enough to support a significant quantity of floating-point arithmetic units on a single-chip. This raises the possibility of exploiting the parallelism of FPGAs for high performance computing applications.

## 2.1.1 The Alpha Data ADM-XRC II Prototyping Board

The designs in this work are implemented in hardware using FPGA prototyping boards supplied by Alpha-Data [Alpha-Data '05]. The boards used are Alpha-Data

ADM-XRC II boards. The ADM-XRC II board is also re-sold by Celoxica as the RC2000 prototyping board [Celoxica '06]. The ADM-XRC II board provides a large FPGA along with up to eight banks of off-chip SRAM memory for storing application data. The boards used in this thesis have six banks of SRAM memory each, providing a total of 12 or 24 Mega-Bytes of memory.

The boards themselves fit on to a ADC-PMC carrier card, which is a 64-bit PCI card that fits into a standard PCI slot in a PC computer. Figure 2-b shows an ADC-PMC card with one ADM-XRC-II card fitted to it. The ADC-PMC card can hold two ADM-XRC-II cards; the spare location can be seen at the front end of the card shown in Figure 2-b marked with "PMC 2". A second ADM-XRC-II card was fitted to this location for the dual FPGA part of this work. The dual FPGA implementation is detailed in Chapter 7. The carrier card can accept up to two ADM-XRC II boards, each with their own FPGA and memory banks. Both boards connect to the host computer's PCI bus through the carrier card. The ADM-XRC II boards used for this work have 6 banks of SRAM memory, and have a six million gate equivalent Xilinx Virtex II FPGA, a XC2V6000FF1152.

The carrier card provides an interconnection between two boards mounted on it. This interconnect was used to build the dual FPGA implementation of the FPGA based Dirac operator. The interconnection consists of 64 wires which can be used by a number of different communications protocols. The choice of communications protocol, which is made by the application designer, depends on the requirements of the application.

#### 2.1.2 ADM-XRC-II Board Support Package

A package consisting of a software application programming interface (API) and a set of hardware macros is supplied with the ADM-XRC-II prototyping board. This gives the designer the ability to do the following:

- Transfer data between the host computer and the SRAM banks.

- Access the SRAM banks from within an FPGA design.

Perform a blocking transfer of 32-bit data words between the FPGA and the host computer. This can be used to synchronise the host computer program with the FPGA design, since neither FPGA nor host can continue until the transfer is complete.

The API is used to write a software program - the host program - that runs on the host computer. The host computer programs the FPGA and manages data transfer to and from the FPGA and its SRAM banks. Hardware macros are included in the FPGA design that allow the host program to access the SRAM banks attached to the FPGA.

All FPGA to host communication is performed over the host computer's PCI bus, to which the ADM-XRC II FPGA board is connected through the carrier card. The ADM-XRC II board includes a PLXPCI chip which handles the complex logic required to interface to a PCI bus. The PLXPCI chip then interfaces with the FPGA design. This eliminates any need for an on-FPGA PCI controller, saving significant FPGA resources. The FPGA to PLXPCI interface logic is quite simple, and is included in the board support package. The Handel-C board support package ensures that the SRAM banks are clocked correctly and handles all data transfer between the host computer and the FPGA and its software.

The SRAM banks cannot be accessed simultaneously by both the host computer and the FPGA design. The status register must be used to synchronise the host and FPGA so that only one accesses the SRAMs at any given time. The following is an outline of the steps taken by a host program running an FPGA design on an ADM-XRC II board:

- Host program sets clocks and loads FPGA design.

- FPGA design performs a blocking status register read, stalling until the host

writes to the status register. The FPGA does not access the SRAMs until after

it has performed a successful read of the status register.

- Host transfers data to SRAM banks and then writes to the status register.

- FPGA reads the status registers and then begins calculation.

- Meanwhile, host performs a blocking status register read stalling the host until the FPGA writes to the status register

- Once the calculation is completed the FPGA writes to status register, the host is now free to read the result from SRAM

This basic scheme prevents simultaneous access to the SRAMs and is the scheme used for the designs in my work. My designs require little FPGA to host communication once the calculation is running making the simple host program sufficient for my needs.

### 2.2 Hardware design languages

In recent years, a number of higher level hardware description languages have been developed as an alternative to the traditional languages of Verilog and VHDL. Each type of tool has a domain of design types to which it is suited. High level languages are better suited to algorithmic hardware implementations whereas conventional HDLs are better suited to lower level more structural designs. This gives high level tools a number of advantages:

- Support for Rapid Prototyping. The time required to generate a working prototype design in a higher level language is significantly less than for conventional tools.

- Higher Level of Abstraction. Conventional HDLs such as VHDL are very

detailed which is very useful for structural designs. Algorithmic

implementations are more difficult in these tools as the design rapidly

becomes unwieldy and complex. Higher level hardware languages help

designers manage complexity in such designs.

These benefits lead to some disadvantages however. The main disadvantage is the relative immaturity of the tools; higher level hardware design languages are quite new and the quality of their development environments is far behind the

development tools for VHDL or Verilog. A good example is the difficulties designers face when trying to use third party Intellectual Property (IP) with Handel-C designs. It is very common for FPGA designs to include a number of precompiled pieces of logic called hardware macros. These hardware macros give designers access to a large library of highly optimised designs.

A very large number of "black box" hardware macros with associated simulation files are available for VHDL/Verilog design tools, however whilst the hardware macros can be easily integrated into a Handel-C design, the Handel-C simulator cannot use the VHDL/Verilog simulation files. It is thus very difficult to simulate Handel-C designs that make use of external hardware macros. The DK environment provides a proprietary simulation mechanism for simulating external hardware macros, but since Handel-C is new, very few hardware macros supply accompanying Handel-C simulator files.

#### 2.2.1 Handel-C

Handel-C is a hardware development language based on the concept of communicating sequential processes (CSP) [Hoare '85]. CSP allows the description of systems that consist of multiple sequential components which are executed in parallel. Communication and synchronisation between the processes are provided by a synchronous message passing system.

Occam is a programming language that is based around the CSP model [INMOS. '84]. Occam provides channels that are used to communicate between parallel processes. Handel-C is a development of the Occam language and its structure is derived from that of Occam. Handel-C provides synchronous communication channels and the ability to specify that code segments be performed sequentially or in parallel.

The syntax of Handel-C is heavily derived from that of the C language. C syntax was chosen as a base for Handel-C syntax since it is a popular and familiar language. The syntax is adapted with some additions that allow it to address the specific architecture of FPGAs. The most significant additions are the ability to specify

parallelism, the ability to specify the size in bits of all variables used in the design and the provision of synchronous channels for communicating between parallel parts of the design. Handel-C can be compiled for the cycle accurate Handel-C simulator or for hardware by compiling it into an EDIF net-list, which is placed and routed for an FPGA using the FPGA manufacturer's place and route tools. The Handel-C compiler can also convert Handel-C source code to VHDL or Verilog source code.

#### 2.2.2 Basic use of Handel-C

```

unsigned int 13 a, b, c, d, e, f, z;

par{

a=a*b;

y=c*d;

z=e*f;

}

```

Figure 2-c. Use of Handel-C par{} block to specify parallelism

This section introduces the most important aspects of Handel-C and demonstrates how they are used for FPGA design. The designer must the width in bits of all variables in Handel-C at compile time. This allows the designer to save significant FPGA resources by keeping variables as small as possible. For example Boolean values can be stored using one bit variables, instead of the full 32 bits that are used in software. Distinct FPGA hardware is created for each variable declared in a Handel-C design; they are not automatically reused like a processor register. The code in Figure 2-c shows the declaration of several thirteen bit wide unsigned integer variables.

```

unsigned 64 a[1000], b[1000], c[1000];

unsigned 16 beta;

unisgned 8 x;

for(x=0; x<1000; x++){

a[x] = a[x] + (b[x] * (c[x] * (unsigned 32)(0 @ beta)));

}</pre>

```

Figure 2-d. A complex expression causing a low clock rate

Every assignment in Handel-C requires one clock cycle to execute. The exception is when statements are placed within a *par* block. The Handel-C *par* construct is the

principal tool for exploiting parallelism in a Handel-C design. Statements grouped within a par block are performed in parallel with each statement using separate hardware. Figure 2-c shows three multiplications performed in parallel in a single clock cycle using a *par* block. In essence, a *par* block specifies a fork-join model of parallel computation.

If the par block were removed from Figure 2-c the multiplications would take three cycles to complete. Removing the par block would not reduce resource requirements however since separate hardware would still be used for each of the three multiplications. A function or a shared expression could be used to perform the three multiplications using the same hardware on three subsequent cycles. This would lower the resource requirements of the design.

```

unsigned 64 a[1000], b[1000], c[1000];

unsigned 64 ct, bt;

unsigned 16 beta;

unisgned 8 x;

ct = c[0] * (unsigned 64)(0 @ beta);

par{

bt = b[0] * ct;

ct = c[0] * (unsigned 64)(0 @ beta);

x=0;

while (x<1000) {

par{

a[x] = a[x] + bt;

bt = b[x+1] * ct;

ct = c[x+2] * (unsigned 64)(0 @ beta);

x++;

}

```

Figure 2-e. Pipelined and parallelized Handel-C loop

Figure 2-d shows a code fragment where every item in an array must be updated. However the update logic is complex, and causing a slow clock rate. The poor clock rate can be improved by splitting the update into several steps. These steps can be parallelised using pipelining, as shown in Figure 2-e. By splitting the single complex assignment into three stages the clock rate of the design has improved significantly, and since the three stages are pipelined, the number of cycles required to update the array has not increased significantly. The code in Figure 2-e has also significantly

improved performance by updating the loop counter in parallel with the loop body, whereas in Figure 2-d it is updated sequentially.

## 2.2.3 Data Storage in Handel-C

Most FPGA designs cannot store all their data in register type storage; usually some form of array type storage is required. FPGAs provide three types of array storage; arrays of registers, distributed RAM and block RAM.

#### Register arrays

Register arrays are constructed from sets of registers and are the most flexible type of array storage, since there are no parallel access restrictions except that only one write can be made to each element in a single clock cycle. However they also consume far more resources than either of the RAM storage types, due to the multiplexers required to control access to the array. Arrays of registers should not be used except when absolutely necessary, or when the arrays involved are very small (around four to six elements).

#### **Distributed RAM**

Distributed RAM is constructed only from LUTs and uses no flip flops at all (see section 2.1 for an explanation of FPGA technology). Distributed RAM uses substantially less FPGA resources compared with register arrays, but at the cost of a restricted number of possible parallel accesses. Distributed RAM can be either single or dual ported. Single ported RAM only allows one access (either a read or a write) to the entire RAM per clock cycle. Dual ported RAM is created using two identical parallel distributed RAMs, so it is a less efficient storage mechanism than single ported RAM. Dual ported distributed RAM allows two reads or one read and a write per cycle. It is not possible perform two writes to a dual ported distributed RAM in a single clock cycle.

#### **Block RAM**

Block RAM is constructed using the on-chip 18-kilobit block RAMs that are part of recent Xilinx FPGAs, starting with the Virtex II family. Block RAM is true dual ported RAM, in that it allows two operations of any type, including two writes, per

cycle. The dual porting of block RAM has no extra cost, as is the case for dual ported distributed RAM.

Access to block RAM is through a one cycle pipeline. To read data from a block RAM the data address is presented to the block RAM, which then writes the data into output registers attached to the block RAM ports. Thus the data is available for use in the next clock period. This one cycle pipeline makes block RAM access more complicated than accessing distributed RAM, which has single cycle access characteristics. To hide this complexity Handel-C clocks block RAMs using a double speed clock, which makes the block RAMs seem to have single cycle access characteristics. Unfortunately this tends to severely limit the clock rate of Handel-C designs that use block RAMs. Later versions of Handel-C include a compiler optimisation that converts block RAMs to pipelined access if data is only read from a block RAM into a single register that is not written to from anywhere else in the design. This optimisation improves clock rate significantly for Handel-C designs that use block RAM.

## 2.3 Number Representations

IEEE floating point is the standard approach for performing non-integer calculations and is implemented on most commodity processors. Log arithmetic, also frequently referred to as the Logarithmic Number System (LNS), is an alternative approach to these calculations that uses fixed point logarithms to represent non-integer numbers. Log arithmetic requires vastly fewer resources for multiplication and division compared with IEEE floating point but addition and subtraction become significantly more complicated. When this project began there were no available options for performing conventional floating point on FPGAs, however log arithmetic was available for use on the project. Consequently it was decided to investigate this system.

#### 2.3.1 Single Precision Log and Floating Point

The logarithmic arithmetic designs use commercial LNS cores from the High-Speed Logarithmic Arithmetic system (HSLA) by Matousek et al [Matousek '02]. These are 32-bit logarithmic cores, which support the full range of exceptions from the IEEE

|                                        | LNS Adder | Underwood Adder |

|----------------------------------------|-----------|-----------------|

| Slices                                 | 1648      | 496             |

| Multipliers                            | 8         | 0               |

| Block RAM                              | 28        | 0               |

| Latency (Clock cycles)                 | 8         | 13              |

| Clock Rate (MHz)                       | 90        | 165             |

| Pipes per FPGA (Xilinx Virtex-II-6000) | 10        | 68              |

Table 2-a. Comparison of the resource requirements of *two* log arithmetic adder pipelines and a comparable IEEE floating point adder pipeline floating point standard. The cores are highly-optimized for both performance and space.

Table 2-a, Table 2-b and Table 2-c show the resource requirements of the LNS adder, multiplier and divider respectively compared with the requirements for comparable IEEE arithmetic units published by Underwood [Underwood '04a]. The pipeline latencies of the Underwood cores are variable. The cores are designed so that the pipeline latency can be reduced however this also reduces the maximum clock rate the cores can run at. Short pipeline latencies are desirable for designs where there are a lot of dependencies between calculations. Using arithmetic cores with long pipeline latencies for such designs can hurt overall performance since the arithmetic pipelines will spend a lot of time waiting for the results of previous calculations.

Logarithmic arithmetic has a clear advantage for multiplication and division. The LNS multiplier is substantially smaller than Underwood's multiplier and has a lower latency. In addition the fully pipelined LNS divider returns similar performance to Underwood's divider but uses less than 5% of the resources and has a much lower

|                                        | LNS Multiplier | Underwood Multiplier |

|----------------------------------------|----------------|----------------------|

| Slices                                 | 83             | 598                  |

| Multipliers                            | 0              | 4                    |

| Block RAM                              | 0              | 0                    |

| Latency (Clock cycles)                 | 1              | 16                   |

| Clock Rate (MHz)                       | 250            | 124                  |

| Pipes per FPGA (Xilinx Virtex-II-6000) | 407            | 36                   |

Table 2-b. Comparison of the log arithmetic multiplier and a comparable IEEE floating point multiplier

#### latency.

The penalty for the small and low latency LNS multiplier and divider is that a pair of log adders requires 66% more slices than a pair of IEEE adders, and a significant quantity of block RAM and hardware multipliers. This block RAM requirement means a maximum of 10 log adder pipelines can fit on the Xilinx Virtex-II-6000 FPGA used in this thesis. However ten log adder pipelines use only 25% of slices on the Xilinx Virtex-II-6000 FPGA, leaving plenty of space for control logic and other arithmetic units.

The resource requirements for the LNS cores favour applications that have a high proportion of multiplications compared with additions. Also the very small size of the divider is a particular advantage for applications which use division only rarely. The lattice QCD conjugate gradient solver implemented in this thesis is an example of such an application. A large IEEE divider is a waste of resources in such designs. Section 3.4 gives an overview of the history and development of logarithmic arithmetic, and compares the current state of the art for floating point and log arithmetic cores.

|                                           | LNS Divider | Underwood Divider |

|-------------------------------------------|-------------|-------------------|

| Slices                                    | 82          | 1929              |

| Multipliers                               | 0           | 0                 |

| Block RAM                                 | 0           | 0                 |

| Latency (Clock cycles)                    | 1           | 37                |

| Clock Rate (MHz)                          | 250         | 100               |

| Pipes per FPGA<br>(Xilinx Virtex-II-6000) | 412         | 17                |

Table 2-c. Comparison of the resource requirements of the log arithmetic divider and a comparable IEEE floating point divider

The Matousek cores were chosen to implement the logarithmic arithmetic FPGA implementations of the lattice QCD Dirac operator and the logarithmic arithmetic conjugate gradient application that are described in Chapter 5. The above comparison of the Matousek cores with floating point arithmetic cores and the comparison between the Matousek cores and alternative logarithmic arithmetic cores in section 3.4.7 show that they are competitive with alternative systems. When the work described in this thesis started the Matousek cores were the only non-integer arithmetic cores available to the project, consequently they were chosen as the best option. During the project single precision floating point arithmetic cores became available however work on the logarithmic arithmetic cores was well advanced by this time. Upon completion of the log arithmetic designs described in Chapter 5, the Moloney double precision floating point cores became available [Moloney '04]. Since double precision arithmetic is the standard arithmetic system for high performance computing applications, these cores were chosen for further work, instead of investigating single precision floating point arithmetic cores.

#### 2.3.2 Double Precision IEEE Floating Point

The IEEE double precision implementations in this work use Moloney's cores

[Moloney '04]. The cores are IEEE compliant, fully pipelined and highly optimized. They achieve good clock rates with short pipeline latencies, which is particularly important for applications with long chains of data dependencies. In such applications arithmetic units must often wait for operands which are the output of previous operations. This causes the arithmetic units to lie idle for a significant portion of the time. If the arithmetic pipeline latencies are long then the waiting time is increased, causing a loss in performance.

Table 2-d, Table 2-e and Table 2-f show performance comparisons for the double precision adder, multiplier and divider compared with cores published by Underwood [Underwood '04a]. In each case, the Moloney units compare well with the Underwood units. The Moloney adder has a slower clock rate than the Underwood adder, however its pipeline is significantly shorter and it uses fewer resources. Similarly the Moloney multiplier has a shorter pipeline latency and a slower clock rate than the Underwood cores. The Moloney core also uses significantly fewer FGA resources.

The Underwood cores implement de-normalised number handling which requires significant quantities of FPGA resources. I use a version of the Moloney cores that do not handle de-normalised numbers which reduces resource requirements compared with other versions that do handle de-normalised numbers. De-normalised number handling is not needed for lattice QCD calculations, since the range of the numbers used is limited. De-normalised number handling is important in applications where very small numbers are involved; without de-normalised number handling, any results smaller than the smallest represent-able normalised value will underflow, that is they will be set to zero. De-normalised numbers fill in the "gap" between the smallest normalised number and zero and reduce the incidence of underflow where calculations are performed involving numbers with very small magnitudes.

The two divider cores are very different in their implementations. The Moloney core is designed for systems where division is used very infrequently, so it was designed to be small and to be able to perform a single divide within a small number of cycles. However it is not pipelined so it can only perform one divide at a time. In contrast

|         | Moloney             | Underwood           |

|---------|---------------------|---------------------|

| Slices  | 937                 | 1090                |

| MHz     | 110 (Speed grade 6) | 125 (Speed Grade 5) |

| Latency | 6                   | 14                  |

Table 2-d. Comparison of double precision adders

|            | Moloney             | Underwood           |

|------------|---------------------|---------------------|

| Slices     | 825                 | 1607                |

| Mult 18x18 | 9                   | 9                   |

| MHz        | 114 (Speed grade 6) | 105 (Speed grade 5) |

| Latency    | 7                   | 20                  |

Table 2-e. Comparison of double precision multipliers

|         | Moloney            | Underwood          |

|---------|--------------------|--------------------|

| Slices  | 1789               | 6858               |

| MHz     | 95 (Speed grade 6) | 83 (Speed grade 5) |

| Latency | 36 (Not Piped)     | 67 (Pipelined)     |

Table 2-f. Comparison of selected dividers

the Underwood divider is designed for systems where there is a high demand for divide operations. The Underwood divider is fully pipelined, which is unusual for a floating point divider. It has a long pipeline latency so it takes twice as long to perform a single divide operation, but being fully pipelined it has a throughput over 30 times greater than the Moloney core. The cost of this performance is that it is nearly 4 times larger than the Moloney divider.

The Moloney divider was used to implement a double precision version of the lattice QCD conjugate gradient solver. Divides constitute a tiny fraction of the floating point operations in this application. Two divides are issued per iteration of the main application loop, and several thousand cycles separate each issue. Thus a small divider with relatively poor performance is far better suited to the needs of the application that a large divider with unnecessarily high performance. Consequently the Moloney divider is far better suited to the needs of the conjugate gradient applications.

### 2.4 Summary

This chapter has introduced the most important technologies that have been used in this work, including FPGAs, FPGA development boards, high level hardware design languages and the non-integer arithmetic FPGA cores used in my designs. The next chapter introduces lattice QCD, the application that is studied in this work, together with an extensive survey of the literature relating to lattice QCD computing machinery and to non-integer arithmetic on FPGAs.

# **Chapter 3**

# **Literature Survey**

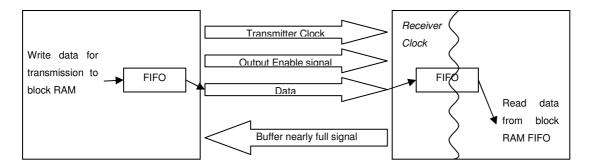

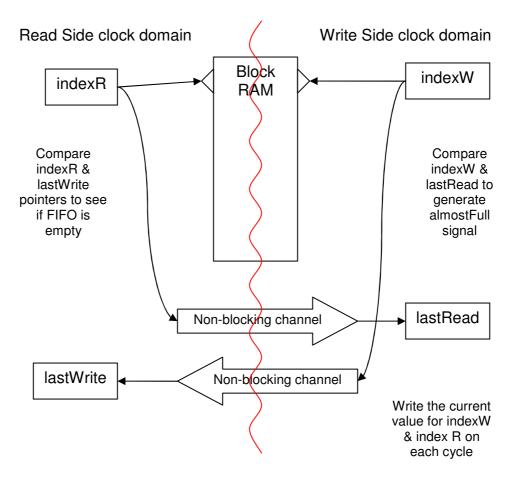

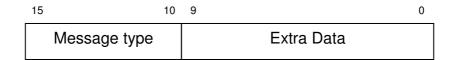

Lattice QCD is a significant high profile high performance computing application, making it an ideal example application for evaluating a platform's suitability for high performance computing. Creating computing machinery for lattice QCD is the focus of significant world-wide research effort. By comparing my results with this body of research, I am able to draw comparisons between FPGAs and the state of the art for high performance computing.