## Vectorization for Accelerated Gather/Scatter and Multibyte Data Formats

by Andrew Anderson

Dissertation

Submitted to the School of Computer Science and Statistics in partial fulfillment of the requirements for the degree of

> Doctor of Philosophy (Computer Science)

School of Computer Science and Statistics

TRINITY COLLEGE DUBLIN

January 2016

## Declaration

I, the undersigned, declare that this work has not previously been submitted to this or any other University, and that unless otherwise stated, it is entirely my own work.

.....

Andrew Anderson Dated: January, 2016

## Permission to Lend and/or Copy

I, the undersigned, agree that Trinity College Library may lend or copy this Dissertation upon request.

.....

Andrew Anderson Dated: January, 2016

### Abstract

SIMD extensions to the instruction sets of general purpose processors have become widespread, and SIMD width and the capabilities provided by the hardware are steadily increasing with newer processor generations.

This thesis tackles two challenges faced by compilers when generating code for modern SIMD extensions: SIMD code generation for interleaved memory access patterns, and SIMD code generation for custom types not provided by hardware.

On the topic of SIMD code generation for interleaved memory access, we address strided array access specifically, and propose and evaluate a technique for the generation of SIMD code to gather and scatter data elements between memory and SIMD registers. Our technique extends a prior state of the art technique to support a wider class of interleaved memory access.

On the topic of SIMD code generation for custom datatypes, we propose and evaluate a vectorized code generation approach which supports reducedprecision floating point number formats along a continuum between native types.

We demonstrate that compilers can generate efficient SIMD code for both challenges using modern SIMD extensions, without requiring special hardware support beyond the general-purpose data movement and reorganization features already present in a variety of modern SIMD-enhanced general purpose processors.

## Acknowledgements

Many thanks are due first to family and friends for their support and encouragement during my studies.

While working on my PhD I spent much time on several very fulfilling teaching positions, which I enjoyed greatly. Thanks are due in particular to David, Andrew, Jonathan, and Glenn for making this possible.

Thanks are especially due to my colleagues who made the lab both an entertaining and an intellectually stimulating environment in which to work: Servesh, Aravind, Martin, Mircea, Shixiong, and others.

Much of the research and investigation I carried out during the first two years of my PhD was in collaboration with Avinash, who was never hesitant to discuss ridiculous ideas which couldn't possibly be made to work.

Finally, it is my great pleasure to thank David, my supervisor, without whose guidance this thesis would not have been possible. David was always available to discuss hare-brained schemes and divine which components were actually useful and interesting, in addition to being a boundless source of advice and knowledge on many topics, both research related and not. Thanks to his patience and understanding, my journey to PhD was smoother than it had any right to be.

## Contents

| 1 | Intr | oductio | on                                                    | 17 |

|---|------|---------|-------------------------------------------------------|----|

|   | 1.1  | Challe  | enges                                                 | 18 |

|   | 1.2  | Thesis  | Structure                                             | 18 |

|   | 1.3  | Contr   | ibutions                                              | 19 |

|   | 1.4  | Collab  | porations and Published Work                          | 20 |

| 2 | Bacl | kgroun  | d & Literature Review                                 | 21 |

|   | 2.1  | Review  | w of Features of SIMD Hardware                        | 22 |

|   |      | 2.1.1   | SIMD-Enhanced GPPs versus Traditional Vector Machines | 23 |

|   |      | 2.1.2   | SIMD versus Out-of-Order Superscalar Execution        | 24 |

|   | 2.2  | Autor   | natic Vectorization on General Purpose Processors     | 25 |

|   |      | 2.2.1   | Capabilities of Vectorizing Compilers                 | 25 |

|   |      | 2.2.2   | Trends in SIMD Width and Memory Access                | 26 |

|   |      | 2.2.3   | The Problem of Non-Consecutive Memory Access          | 27 |

|   | 2.3  | Overv   | view of Automatic Vectorization                       | 28 |

|   |      | 2.3.1   | Loop Vectorization                                    | 29 |

|   |      | 2.3.2   | Superword Level Parallelism                           | 29 |

|   |      | 2.3.3   | Analysis and Program Transformation                   | 30 |

|   |      | 2.3.4   | Vectorization of Control Flow                         | 31 |

|   |      | 2.3.5   | Domain-Specific SIMD Languages and Compilers          | 31 |

|   | 2.4  | Memo    | ory Access with Multimedia Extensions                 | 32 |

|   |      | 2.4.1   | Spatial Locality of Access                            | 32 |

|   |      | 2.4.2   | Alignment                                             | 33 |

|   | 2.5  | Appro   | oximate Computing                                     | 33 |

|   |      | 2.5.1    | Floating Point Programs with Reduced Accuracy             | 34 |

|---|------|----------|-----------------------------------------------------------|----|

|   |      | 2.5.2    | Customized Data Storage Formats                           | 34 |

|   |      | 2.5.3    | Multibyte Floating Point                                  | 35 |

|   | 2.6  | Summ     | nary and Directions for Improvement                       | 36 |

| 3 | Vect | torizati | on of Static Affine Interleaving                          | 37 |

|   | 3.1  | Mode     | lling Arrays and Array Access                             | 38 |

|   |      | 3.1.1    | Notation and Presentation                                 | 40 |

|   | 3.2  | Techn    | ique                                                      | 42 |

|   |      | 3.2.1    | Enabling Interleaved Access: Automatically Vectorizing    |    |

|   |      |          | a Single Strided Access                                   | 42 |

|   |      | 3.2.2    | Exploiting Spatial Locality:                              |    |

|   |      |          | Grouping Multiple Interleaved Accesses                    | 44 |

|   |      | 3.2.3    | Dealing with Store-Side Gaps                              | 48 |

|   | 3.3  | Optim    | nization                                                  | 49 |

|   |      | 3.3.1    | Eliminating Permutations I:                               |    |

|   |      |          | Executing Original Loop Iterations Out-Of-Order           | 50 |

|   |      | 3.3.2    | Eliminating Permutations II:                              |    |

|   |      |          | Simultaneously Resolving Collisions for Multiple Accesses | 52 |

|   |      | 3.3.3    | Statically Determining Lane Collisions                    | 54 |

|   |      | 3.3.4    | Reassociation of Blend Instructions                       | 55 |

|   |      | 3.3.5    | Eliminating Blends: Merging Multiple Blend Instructions . | 58 |

|   | 3.4  | Evalu    | ation                                                     | 58 |

|   |      | 3.4.1    | Time Complexity of Generated Code                         | 60 |

|   |      | 3.4.2    | Simple Canonical Technique (Algorithms 1 and 2)           | 61 |

|   |      | 3.4.3    | Out-of-Order Technique (Algorithms 3 and 4)               | 61 |

|   |      | 3.4.4    | Collision Resolving Technique (Algorithms 5 and 6)        | 61 |

|   |      | 3.4.5    | Comparison with Nuzman et al                              | 63 |

|   |      | 3.4.6    | Native Code Generation                                    | 64 |

|   |      | 3.4.7    | Experimental Evaluation                                   | 65 |

|   | 3.5  | Discu    | ssion of Results                                          | 66 |

|   |      | 3.5.1    | Performance Limits                                        | 66 |

|   |     | 3.5.2    | Effect of Reordering                                    | . 67  |

|---|-----|----------|---------------------------------------------------------|-------|

|   |     | 3.5.3    | Relation of Speedup to Stride                           | . 72  |

|   |     | 3.5.4    | Variability of Scalar Code                              | . 72  |

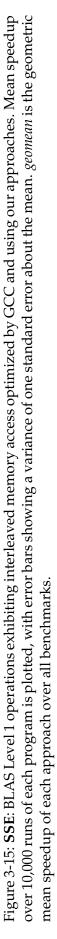

|   |     | 3.5.5    | Real-World Benchmarking (SSE)                           | . 73  |

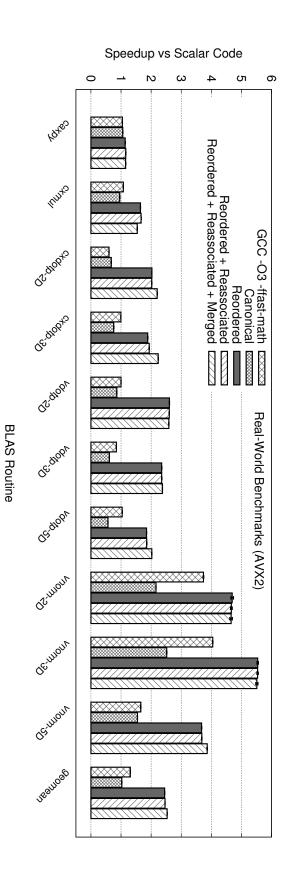

|   |     | 3.5.6    | Real-World Benchmarking (AVX2)                          | . 75  |

|   |     | 3.5.7    | Comparison with Hand-Tuned and Reference BLAS           | . 76  |

|   | 3.6 | Relate   | ed Work                                                 | . 77  |

|   |     | 3.6.1    | Superword Level Parallelism                             | . 78  |

|   |     | 3.6.2    | Alignment                                               | . 79  |

|   |     | 3.6.3    | SPIRAL                                                  | . 80  |

| 4 | Vec | torizati | on of Multibyte Floating Point Data Formats             | 85    |

|   | 4.1 | IEEE-    | 754 Floating Point                                      | . 86  |

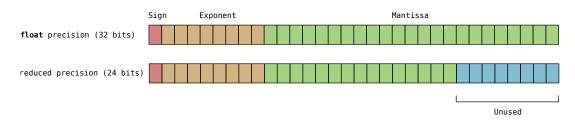

|   | 4.2 | Thoug    | ght Experiment: 24-bit float                            | . 86  |

|   | 4.3 | A Sch    | eme for Reduced-Precision Floating Point Representation | . 88  |

|   |     | 4.3.1    | Practical Multibyte Representations for IEEE-754        | . 89  |

|   |     | 4.3.2    | Simple Scalar Code Approach                             | . 90  |

|   | 4.4 | Readi    | ng from Reduced-Precision Representations               | . 91  |

|   | 4.5 | Writir   | ng to Reduced-Precision Representations                 | . 92  |

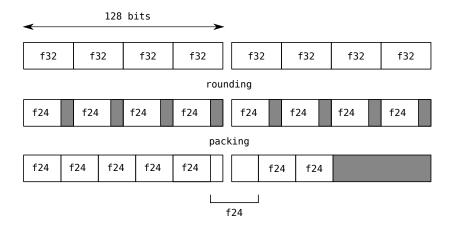

|   |     | 4.5.1    | Vectorized I/O with Multibyte Representations $\ldots$  | . 92  |

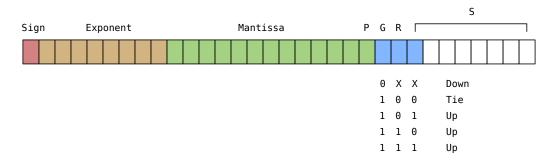

|   |     | 4.5.2    | Rounding                                                | . 94  |

|   |     | 4.5.3    | Treatment of Special Values                             | . 96  |

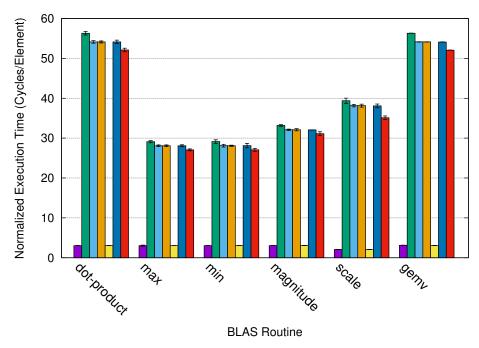

|   | 4.6 | Perfo    | rmance Evaluation                                       | . 97  |

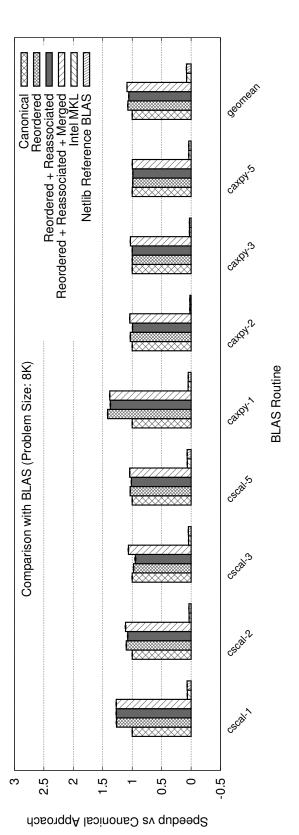

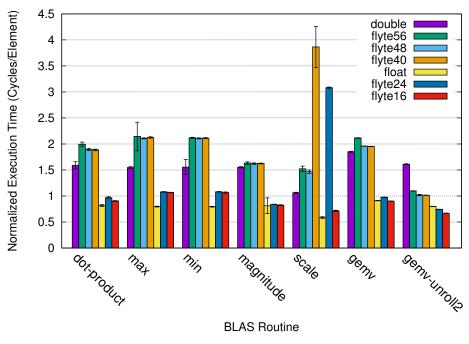

|   |     | 4.6.1    | BLAS Level 1 Evaluation                                 | . 98  |

|   |     | 4.6.2    | BLAS Level 2 Evaluation                                 | . 100 |

|   | 4.7 | Relate   | ed Work                                                 | . 102 |

|   |     | 4.7.1    | The Approach of Jenkins et al.                          | . 102 |

|   | 4.8 | Concl    | usion                                                   | . 103 |

| 5 | Con | clusio   | n and Final Thoughts                                    | 105   |

|   | 5.1 | Futur    | e Work                                                  | . 105 |

|   |     | 5.1.1    | Generalized Interleaved Access                          | . 105 |

|    |      | 5.1.2          | Runtime Code Generation              | 106        |

|----|------|----------------|--------------------------------------|------------|

|    |      | 5.1.3          | Finer Granularity of Storage Formats | 106        |

|    | 5.2  | Final          | Thoughts                             | 107        |

| Aj | ppen | dices          |                                      | 108        |

| Α  | Ider | ntities f      | for Rounding                         | 109        |

|    |      |                |                                      |            |

|    |      | A.0.1          | Arithmetic Rounding I                | 109        |

|    |      |                | Arithmetic Rounding I                |            |

|    |      | A.0.2          | Ŭ                                    | 110        |

|    |      | A.0.2<br>A.0.3 | Arithmetic Rounding II               | 110<br>111 |

# **List of Figures**

| 3-1 | The target intermediate representation for code generation                                            | 41 |

|-----|-------------------------------------------------------------------------------------------------------|----|

| 3-2 | Vectorizing interleaved access using mapped register sets                                             | 42 |

| 3-3 | Sharing load-mapped/store-mapped register sets to exploit spa-                                        |    |

|     | tial locality                                                                                         | 46 |

| 3-4 | Effect of reordering original loop iterations to match data layout.                                   | 50 |

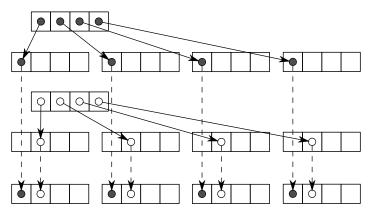

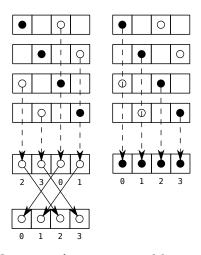

| 3-5 | Algorithm 5. Our transformation enables vertical composition                                          |    |

|     | with the blend instruction of colliding memory accesses with                                          |    |

|     | a single transformation of the mapped register set. One access                                        |    |

|     | is out-of-order under vertical composition with blend after data                                      |    |

|     | layout transformation (left side). However, the vectorization can                                     |    |

|     | be legalized with a single permute as shown, to ensure the order                                      |    |

|     | of elements in each register is the same                                                              | 54 |

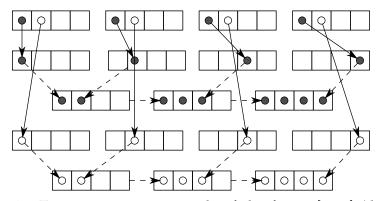

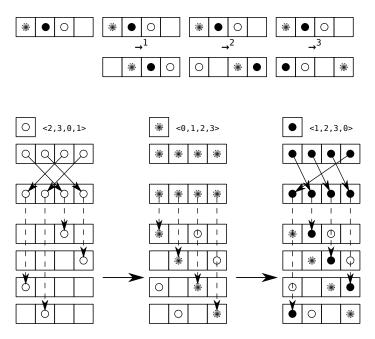

| 3-6 | Algorithm 6. Accesses $a[4 * i + 2]$ (light dots), $a[4 * i]$ (patterned                              |    |

|     | dots), and $\mathtt{a}[\mathtt{4}\ast\mathtt{i}+\mathtt{1}]$ (black dots). Desired store order at top |    |

|     | with rotated store order underneath. Required permutation of                                          |    |

|     | each access to obtain rotated store order indicated with permute                                      |    |

|     | masks. Heavy arrows at bottom show the evolution of the store-                                        |    |

|     | mapped register set as each access is interleaved in. Final store-                                    |    |

|     | mapped register set before inverse rotation is shown at bottom                                        |    |

|     | right                                                                                                 | 55 |

| 3-7 | Rewrite rule for reassociation of $blend$ instruction sequences                                       | 57 |

| 3-8 | Graphical depiction of data flow before and after merging blend                                       |    |

|     | instructions.                                                                                         | 59 |

| 3-9 | Rewrite rule for merging blend instruction pairs                                                      | 60 |

|     |                                                                                                       |    |

| 3-10 | Primitive operations of Nuzman et al                                | 64 |

|------|---------------------------------------------------------------------|----|

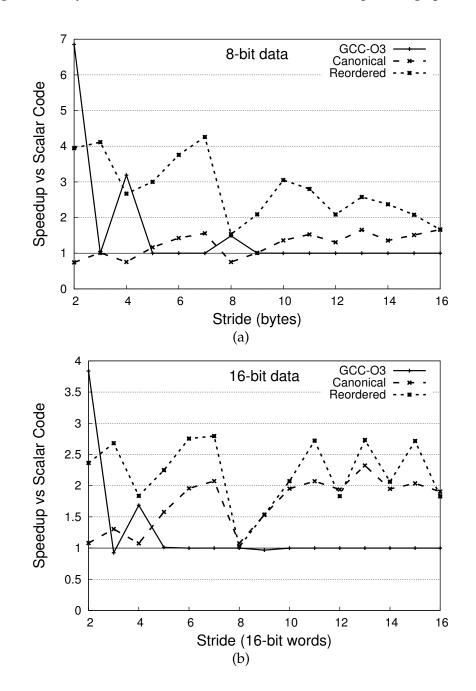

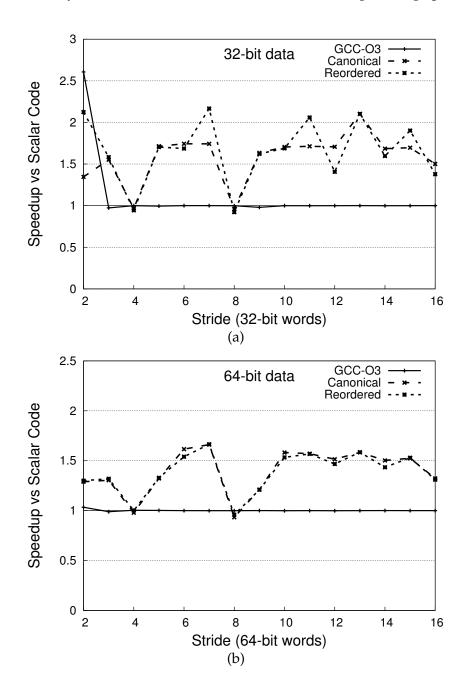

| 3-11 | Synthetic benchmark results: 8-bit and 16-bit gathering operations  | 68 |

| 3-12 | Synthetic benchmark results: 32-bit and 64-bit gathering opera-     |    |

|      | tions                                                               | 69 |

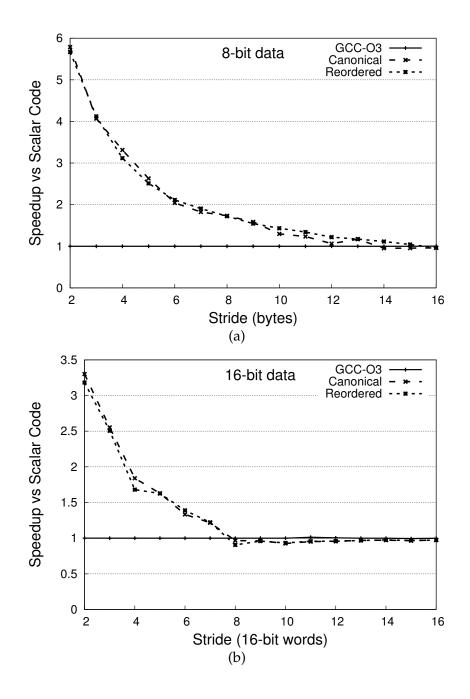

| 3-13 | Synthetic benchmark results: 8-bit and 16-bit scattering operations | 70 |

| 3-14 | Synthetic benchmark results: 32-bit and 64-bit scattering opera-    |    |

|      | tions                                                               | 71 |

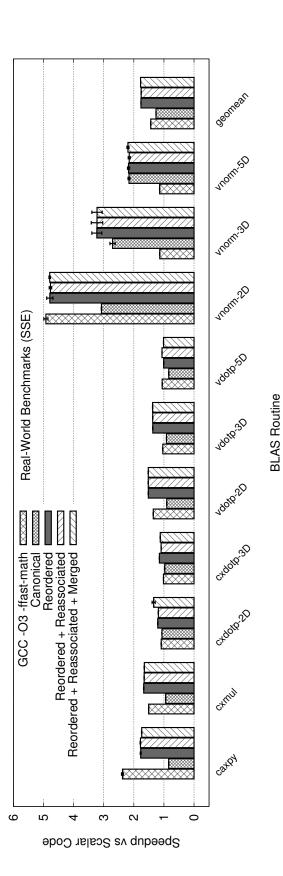

| 3-15 | Real-World Benchmarks (SSE)                                         | 81 |

| 3-16 | Real-World Benchmarks (AVX2)                                        | 82 |

| 3-17 | Reference BLAS/Intel MKL Comparison                                 | 83 |

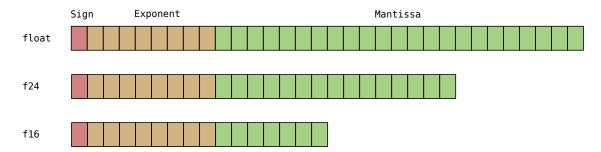

| 4-1  | Unused bit positions in reduced-accuracy results                    | 87 |

| 4-2  | Layout of alternative multibyte floating point formats              | 89 |

| 4-3  | Simple implementation of flyte24 in C++                             | 91 |

| 4-4  | Layout of data in SSE vector registers before format conversion     |    |

|      | (top), after rounding to the desired size (center) and the desired  |    |

|      | layout in memory (bottom).                                          | 93 |

| 4-5  | Rounding to nearest even. Marked bit positions correspond to        |    |

|      | Preguard, Guard, Round, and Sticky bits.                            | 94 |

| 4-6  | Real-world benchmarks                                               | 01 |

# List of Tables

| 3.1 | Time complexity of SIMD interleaving and deinterleaving code | 62 |

|-----|--------------------------------------------------------------|----|

| 3.2 | Summary of dimensions, strides, underlying C types, and vec- |    |

|     | torization realized in benchmarking                          | 73 |

| 4.1 | Supported <i>flyte</i> storage formats for IEEE-754 types    | 90 |

## Chapter 1

## Introduction

SIMD (Single Instruction Multiple Data) execution is a mode of parallel execution where a processor executes a single instruction that operates on multiple values at once. These values are held in wide registers (often referred to as *vector registers*), with each value notionally occupying a specific *lane*, representing the location of the value within the register. Using SIMD instructions, all the values stored in a register can be operated on simultaneously. SIMD instructions are often referred to as *vector* instructions, and in this thesis, the two terms are used interchangably.

For example, on a 4-way SIMD machine, a single SIMD add instruction will simultaneously perform four additions, adding together pairs of values which occupy the same lane in their respective registers to produce four results. SIMD execution is an efficient way to exploit fine-grained parallelism at the instruction level to speed up the execution of programs. The degree of parallelism exploited by a program using vector instructions is known as the *vectorization factor*, written VF for short.

Both x86 and ARM [66] processor families provide extensions with a set of instructions supporting short vector parallelism. Intel's **Streaming SIMD Extensions** (SSE) for x86 and the ARM NEON instruction set both operate on 128-bit vector registers which can be treated as a number of 8-, 16-, 32-, or 64bit *lanes*. Intel's **A**dvanced **V**ector e**X**tensions (AVX) introduced 256-bit vector registers [25], doubling the potential vectorization factor which can be achieved over SSE. Intel's forthcoming AVX-512 extensions will support even longer 512bit vector registers.

### 1.1 Challenges

This thesis tackles two challenges faced by compilers when generating code for modern SIMD extensions. First, in Chapter 3, we address the problem of SIMD code generation for interleaved memory access patterns with strides other than powers of two. Second, in Chapter 4, we address the problem of SIMD code generation for datatypes whose width is not a power of two. Chapter 2 explores some motivation and background for supporting these memory access patterns in vectorized code.

### **1.2 Thesis Structure**

The remainder of this thesis is structured as follows.

In Chapter 2, we present an overview of the capabilities of present-day SIMD hardware, and discuss the area of automatic vectorization in compilers. We are particularly interested in the generation of code for vector memory access. We also explore the relationship between SIMD and approximate computing, with a particular focus on memory access in variable-accuracy algorithms.

In Chapter 3, we propose a new approach to automatic vectorization for non-consecutive memory access patterns. Our approach extends the state of the art, and we achieve significant performance gains on two widespread modern SIMD architectures.

In Chapter 4, we propose a novel, vectorized approach to reduced-precision representation of floating point data. We propose a set of low-precision storage formats, and show that they can be implemented using current SIMD extensions, without requiring specific hardware support. Several formats do not correspond to any available machine type, but we demonstrate that they can be manipulated very efficiently in a vectorized fashion. In our experimental eval-

uation, we find that these formats can be supported with little to no overhead compared to native formats, and in some cases can even result in performance gain. We conclude in Chapter 5, discuss our findings at a more general level, and present some interesting directions for future work.

### **1.3 Contributions**

The principal contributions of this thesis are as follows. We propose a general scheme for the generation of vectorized code for a class of non-contiguous data access which we term *Static Affine Interleaving*. This class of non-contiguous data access encompasses all dense array accesses which have a compile-time constant stride and offset. The state-of-the-art prior work of Nuzman et al. developed a method for the vectorization of the subset of accesses where the stride of access is a power of two [53]. We extend and generalize their approach to support the case of arbitrary compile-time constant strides.

We demonstrate that significant speedup can be obtained from *automatic* vectorization of interleaved accesses at a variety of strides, many of which have previously been considered to require irregular or hand-tailored solutions.

We also propose a scheme for the vectorized implementation of customized multibyte data formats for storage of results with reduced accuracy. Our scheme performs computation using native data formats, and inserts format conversion operations during loading and storing of data. Recent work in the area of reduced-precision representations [33] identified a low-level vectorized approach as likely to have significant value.

We show that efficient vectorized code can be generated to accelerate the conversion between natively supported datatypes and custom multibyte data formats which lack native support. Although conversion of data between formats has significant overheads, we demonstrate that a vectorized implementation of reduced-precision floating point storage formats can achieve speedup even at small scales well outside the supercomputing context where previous results were demonstrated.

## **1.4** Collaborations and Published Work

A modified version of Chapter 3 has been accepted for publication in ACM Transactions on Architecture and Code Optimization.

Andrew Anderson, Avinash Malik, and David Gregg. "Automatic Vectorization of Interleaved Data Revisited". In: *ACM Transactions on Architecture and Code Optimization (TACO)* 12.4 (2015), p. 50

This work arose out of a collaboration with Dr. Avinash Malik on a domainspecific language and compiler designed to support image processing applications. As part of that work, we realized that there was no all-purpose solution to the problem of generating vectorized code for strided memory access. Avinash provided many helpful comments and lent his expertise in analysis and program transformation to initial discussions of the approach. In addition, he incorporated an early implementation of the techniques into a compiler he was developing, and provided feedback on their operation. We also collaborated on the text of the paper accepted by ACM TACO. However, the structure of the techniques and the associated optimizations presented in Chapter 3 are my own work.

## Chapter 2

## **Background & Literature Review**

Automatic vectorization is a family of compiler techniques within the more general field of automatic parallelization. An auto-vectorizing compiler attempts to identify statements or operations in a program which can be executed in parallel using SIMD instructions, and then to transform the program so that those statements or operations are actually performed in parallel using SIMD hardware.

Automatic vectorization in one form or another has been incorporated in compilers for many years, beginning with compilers for vector supercomputers [3, 4, 90]. Starting with the Hewlett-Packard PA-RISC processor family [46], and Sun Microsystems UltraSPARC [36], commodity computer hardware began to include some SIMD capabilities, by extending existing instruction sets with SIMD instructions. Wider availability of SIMD capabilities in commodity hardware [60, 61] has made automatic vectorization an important concern for optimizing compilers.

Many of the challenges of generating vector code stem from the design and implementation of SIMD extensions in general-purpose processors. With this in mind, we have structured this chapter as follows. We first review some literature describing important features and limitations of SIMD hardware, and the context in which SIMD extensions were developed. We then discuss a selection of key publications on automatic vectorization techniques, which have influenced the work presented in this thesis. Finally, we summarize and discuss the specific challenges tackled by this thesis in the context of prior work.

## 2.1 Review of Features of SIMD Hardware

Many microarchitectures in widespread use today provide short vector instructions as an extension of the scalar instruction set to support applications with fine-grained data parallelism [25]. Typically, short vector extensions are implemented in separate functional units, with their own pipeline and register files. They provide parallel versions of scalar arithmetic, data movement, and miscellaneous other functions.

SIMD extensions to the instruction sets of general purpose processors (GPPs) were first developed in response to the evolving need for acceleration of rich multimedia applications, which incorporated computationally heavy tasks such as audio and video decoding [46] and computer vision [22]. As general purpose processors have become faster and more capable, new application areas which benefit from acceleration with SIMD continue to develop. A good example of such an area is computational photography [65].

Diefendorff and Dubey give an early overview of the challenges posed by these multimedia applications, and describe how they were expected to influence processor design [23]. Though almost two decades have passed since the publication of their review, their predictions have largely been borne out. Multimedia applications remain widespread, and general purpose processors have had more and more SIMD capabilities included with each processor generation. Many of the challenges they discuss, such as data reorganization, still pose problems for vectorizing compilers today.

More recently, Talla et al. discuss the design of SIMD extensions and architectural enhancements [79]. They discuss the overheads associated with the implementation SIMD extensions in general purpose processors, and investigate the causes of bottlenecks in vectorized programs. They find that memory access patterns in programs are one of the primary impediments to efficient utilization of SIMD hardware. From Talla et al.:

[...] even though GPPs are enhanced with SIMD extensions to extract DLP in multimedia programs, there is a mismatch between the requirements of media applications (for address generation and nested loops) and the ability of GPPs with SIMD extensions.

#### 2.1.1 SIMD-Enhanced GPPs versus Traditional Vector Machines

Arguably the most important practical difference between SIMD-enhanced general purpose processors and traditional vector machines is in the functionality provided by the memory subsystem.

Traditional vector processors provided rich data access instructions for gather, scatter, and strided memory operations. However, modern SIMD extensions typically provide very poor support for non-consecutive memory access. SIMD instructions on GPPs work best on data that is contiguous in memory, and operating on non-contiguous data requires the generation of additional instructions to perform *data layout transformation* — packing and unpacking data elements between memory and vector registers.

However, real-world programs often manipulate data stored non-consecutively in memory, and have nested loops [79]. To parallelize these programs using SIMD extensions, the compiler must be able to transform the program to map these structures on to the restricted capabilities provided by the hardware. Nuzman and Henderson describe the challenges of multi-platform automatic vectorization in the GCC compiler [52].

Additionally, the length of vector registers in a general purpose processor is typically fixed at a short size. For example, the size of a vector register is 128 bits on Intel SSE and ARM NEON.

#### 2.1.2 SIMD versus Out-of-Order Superscalar Execution

Out-of-order superscalar processors dynamically exploit parallelism in the program while it is executing, by finding independent instructions in the program and executing them in parallel. The parallelization is accomplished entirely in hardware, using complex logic which inspects instructions which are about to be executed, and finds those which can execute in parallel, using the different functional units within the processor. This is in contrast to SIMD execution, where the compiler is responsible for transforming the input program to extract parallelism by mapping multiple scalar operations to a single SIMD operation.

Lee and DeVries, and later, Lee and Stoodley, investigated the merits of SIMD parallel execution compared to out-of-order superscalar execution [44, 45]. As the degree of parallelism present in a program increases, they found that SIMD execution is able to exploit the parallelism more efficiently than out-of-order superscalar execution, while not requiring any more silicon area. From Lee and DeVries [[44]]:

There are two reasons why vector processors are no more area-intensive than superscalar processors. One is that partitioning the register file into vector registers and lanes provides tremendous bandwidth without incurring a large area penalty. The second reason is that the control logic for issuing vector instructions is only slightly more complex than the control logic for scalar issue. In contrast, instruction control in superscalar processors is significantly more complex and thus requires substantially more area to implement.

Kozyrakis and Patterson additionally compare a SIMD architecture with both superscalar and VLIW architectures [37]. They find that for multimedia applications on embedded systems, a SIMD architecture has advantages in performance and power consumption, and has reduced design complexity versus superscalar and VLIW machines. They also found that applications parallelized with SIMD instructions typically have reduced code size compared to superscalar and VLIW parallelism.

## 2.2 Automatic Vectorization on General Purpose Pro-

#### cessors

While a fully comprehensive overview of published work on SIMD is impossible, several review works have been published concerning automatic vectorization using short vector extensions specifically. In an early work,

Cheong and Lam describe the design and implementation of an optimizer which targets the UltraSPARC VIS instruction set [20], and provide a general review of the challenges faced by automatic vectorization.

Krall and Lelait give a high-level overview of compilation techniques for so-called *multimedia processors* (processors incorporating SIMD extensions for the purpose of accelerating multimedia applications) [38].

Ren et al. also discuss the vectorization of applications using SIMD extensions targeted at multimedia applications [67]. Many techniques applied to vectorize programs using short vector extensions were initially developed for traditional long-vector machines [4].

#### 2.2.1 Capabilities of Vectorizing Compilers

Maleki et al. describe an evaluation of production compilers which perform automatic vectorization, aiming to investigate what sorts of programs are difficult for compilers to automatically vectorize, and what the reasons for these difficulties are [49].

Their evaluation covers the open-source GCC compiler, as well as Intel's ICC, and IBM's XLC. They provide a thorough review of the issues that limit automatic vectorization by these compilers in a range of programs drawn from different benchmark suites. A key issue is that of memory access patterns, in particular, programs with non-unit stride memory access.

From Maleki et al.:

Our results show that after 40 years of studies in auto vectorization, today's compilers can at most vectorize 45-71% of the loops in our

synthetic benchmark and only 18-30% in our collection of applications.

Bik et al. provide a detailed overview of the automatic vectorization methods used in the Intel C++/Fortran compiler [12]. They also note that vectorization of non-unit-stride memory references poses significant challenges. According to Bik et al. elaborate instruction sequences may be used to implement nonunit stride memory references, but this method usually does not yield much speedup.

Two reviews have been published which specifically discuss the automatic vectorization capabilities of the GCC compiler: first in 2004 [51] and again in 2006 [54]. Again, non-consecutive memory access patterns are noted as a concern. The initial review notes that non-unit stride memory references incur considerable overhead, and, because of this, the access patterns supported by the vectorizer are limited to consecutive access only. The later review was performed just after the publication of a technique by the same authors which generates efficient code for power-of-two strided access [53]. This technique has remained the state-of-the-art for many years, and at the time of writing is the default method of vectorization for non-consecutive memory accesses in GCC. The work of Nuzman et al. is particularly relevant to this thesis, and is discussed in detail in Chapter 3.

#### 2.2.2 Trends in SIMD Width and Memory Access

There is a global trend towards increasing SIMD width on general purpose processors, exemplified by the introduction of progressively wider vector units in successive generations of processors in the x86 family [25].

Schaub et al. recently investigated the impact of increasing SIMD width on control flow and memory divergence in vectorized code [72]. They find that as SIMD width increases, across a wide range of representative benchmark programs, memory access becomes less uniform and less consecutive. If vectorizing compilers are to be able to exploit the trend in increasing SIMD width for actual performance gain, one of the key challenges is efficient, flexible SIMD code generation for non-consecutive memory access.

#### 2.2.3 The Problem of Non-Consecutive Memory Access

SIMD instructions on modern processors operate on data packed consecutively into vector registers, and typically only provide instructions to load and store data from consecutive memory locations. However, a common data access pattern is where data items that are processed in consecutive operations in a program are stored non-consecutively in memory. Strided array access is a common example of non-consecutive data access.

When automatic vectorization techniques group together operations which use data that is not consecutive in memory, and the processor does not support SIMD operation on non-consecutive data, the compiler must generate code to gather different data elements together into a vector register for reads, or scatter the contents of a vector register over memory, for writes. We refer to this as the problem of non-consecutive memory access.

Due to the difficulty of dealing with memory access in the generation of vectorized code, Chang and Sung propose augmenting processors with special hardware to support irregular, misaligned, and strided memory access [17]. However, until robust hardware support for non-consecutive access with SIMD extensions becomes widespread, the task of generating fast code for non-consecutive memory access falls to the compiler.

While some automatic vectorization techniques have been proposed which can deal with non-consecutive data access, they typically work by attempting to circumvent the lack of hardware support for non-consecutive data access. Some techniques attempt to reorganize the program so that access becomes consecutive [42], but this is not always possible.

Other techniques insert extra instructions in the program to rearrange data in memory so that the data elements operated on by SIMD instructions are stored consecutively, but this has significant overhead [48]. Because of the widespread lack of hardware gather/scatter support, many vectorization techniques operate with the assumption that all data access is consecutive. A broad selection of these techniques are discussed in Section 2.3. If a region of the program contains non-consecutive data access, these techniques are unable to vectorize that region. A paper at the 2004 GCC Developers Summit [51] describes the status of automatic vectorization in the open-source GCC compiler. At that time, the compiler would only vectorize regions with consecutive data access.

In 2006, Nuzman et al. described a technique by which the compiler could generate efficient SIMD instructions to perform strided array access, without requiring hardware support for gathering or scattering operations. The technique has been the state-of-the-art approach for loop vectorization, and is the default method for vectorization of strided array access in GCC at present. However, the technique can only generate SIMD code for power-of-two strided access [53].

## 2.3 Overview of Automatic Vectorization

Automatic vectorization relies on many pieces of compiler technology in addition to the techniques which actually perform the translation of programs to vector form. In this section, we review the literature on supporting technologies for vectorization. These include program analysis, theoretical models of computation, and code and data restructuring techniques. We also discuss some optimization challenges which are particularly important for vectorized programs, such as optimization of data permutations and locality of data access.

Over the years, many approaches to automatic vectorization have been proposed. So many, in fact, that recent work has applied machine learning techniques to the problem of simply *choosing* which vectorization techniques to apply to particular programs [78]. Broadly speaking, the approaches to automatic vectorization which are implemented in compilers for general-purpose programming languages such as C and C++ belong to one of two families.

#### 2.3.1 Loop Vectorization

One family of approaches deals with cyclic control structures which repeatedly iterate a set of operations. Multiple instances of the same operation are grouped together from successive iterations of the control structure to form a single SIMD operation. We refer to this family of approaches as *loop vectorization*.

Loop vectorization targets loops specifically, with the aim of performing multiple loop iterations in parallel by transforming the instructions in the loop into vectorized form. Early vectorizers focused exclusively on vectorizing loops [3], and the area is still the subject of much work.

For nested loops, the innermost loop is the usual target for vectorization, but vectorization of outer loops can sometimes yield better results [85]. The topic of vectorization of outer loops is revisited by Nuzman and Zaks for modern short vector extensions [55].

Karrenberg and Hack propose a holistic approach to vectorization of whole functions, encompassing control and data flow [35]. Their approach can be seen as an evolution of loop vectorization. However, their approach, like each of the others cited, assumes consecutive memory access.

#### 2.3.2 Superword Level Parallelism

Another family of approaches deals with straight-line code, which performs a set of operations only once. Multiple *isomorphic* operations in a subgraph of the program, which perform the same computation but work on different data elements, are selected. These are grouped together into a single SIMD operation. We refer to this family of approaches as *superword level parallelism* or SLP. Vectorization techniques based on SLP [42] incorporate a tactic which can handle a restricted case of non-consecutive memory access. SLP attempts to transform programs so that memory accesses *become* consecutive, for example, by searching for an unrolling factor for scalar loops which results in a dense memory access pattern in the vectorized loop. It is not always possible to transform the program in such a way.

For loops, for example, an unrolling factor that makes strided access consective can only be found if the scalar version of the loop touches every element of each accessed array region within VF loop iterations [42].

Park et al. [59] propose a "SIMD Defragmentation" approach which tries to extract parallelism at the level of subgraphs of operations within the program, similar to SLP. However, their approach does not address non-consecutive memory access beyond what was proposed in Larsen and Amarasinghe's original SLP paper.

Very recently, Porpodas et al. introduced a flexible version of SLP which can parallelize subgraphs which are not perfectly isomorphic by introducing extra operations to make them so [64]. However, like Park et al., they do not address non-consecutive memory access beyond what was proposed in the original SLP paper.

#### 2.3.3 Analysis and Program Transformation

Automatic vectorization usually proceeds from the structure of data dependences within the program. A dependence analysis is used to detect operations or regions in the program which can run in parallel [57]. Many classical code optimization and reorganization techniques can applied before vectorization to make the program easier to vectorize [50, 5]

The polyhedral model is an important framework for this kind of analysis [21]. In the polyhedral model, data dependences between statments in loops are modeled as a dependence polyhedron, that is, by relations between sets of points in an integer vector space where each point represents a loop iteration (the iteration space). This representation is transformed and manipulated to reorganize loops so that parallelism is exposed and locality is improved. Optimizers based on the polyhedral model are used in LLVM [30] and in GCC [63, 77, 81]. Vectorization can be represented in the polyhedral model, and Trifunovic et al. apply the model to generate vectorized code for loop nests [80]. However, the focus of their work is high-level optimization of the control structure, and the generation of code for the data access in the reorganized loops is not addressed.

#### 2.3.4 Vectorization of Control Flow

Auto-vectorization approaches can also be applied to vectorize control flow, such as conditional branches generated by if-statements, within a program. Previous work extends SLP [75] to enable it to vectorize control flow by converting conditional expressions in the scalar code into predicated vector expressions (if-conversion).

Later work by Shin et al. introduced an approach which takes advantage of a particular type of SIMD instruction called BOSCC (Branch On Superword Condition Code) to represent control flow in vectorized programs [76].

#### 2.3.5 Domain-Specific SIMD Languages and Compilers

A common tactic to ease the task of producing SIMD code is to use domainspecific languages which either provide explicit-SIMD programming constructs, or programming constructs that can be mapped to efficient SIMD code by the compiler.

SPL [89] is a domain-specific language for describing transformations used in digital signal processing. The associated compiler system, SPIRAL [27], generates fast SIMD code to implement the transformations. Research on the SPI-RAL system has resulted in several advances in SIMD code generation, particularly in the area of SIMD permutations [28].

Some approaches propose to extend C and similar languages with explicit SIMD language features [15]. These include Intel's ispc, which is a language

and compiler system for SIMD [62] that also extends C with SIMD language features. The IVL language and compiler is another explicit-SIMD programming system based on ispc [47].

The Halide language [65] is a project that differs from other approaches by decoupling the specification of algorithms from their schedule. Halide allows programmers to explicitly request vectorized execution of regions of their program, in addition to other methods of parallelization.

All of these approaches aim to improve the performance of SIMD programs by giving the programmer more ways to structure their code to explicitly take advantage of SIMD hardware.

## 2.4 Memory Access with Multimedia Extensions

There are several concerns specifically with memory access in programs which make use of multimedia extensions. In this section we review some approaches to concerns such as alignment, locality of access, and data layout transformation.

#### 2.4.1 Spatial Locality of Access

Spatial locality of access is a major concern in optimized code generation, particularly on microarchitectures with an extensive cache. When an access causes data to be fetched into the cache, subsequent accesses very close to the first are likely to result in cache hits, speeding up the program by eliminating costly main memory accesses. To exploit this arrangement, compilers optimize for spatial locality by rearranging the program so that data frequently accessed together in the program are stored closer together in memory.

Shin et al. discuss optimizing for spatial locality in vectorized code specifically [73], and propose some techniques to optimize locality using vector registers [74]. The polyhedral model also deals very comprehensively with locality concerns at a more general loop level [14, 13].

#### 2.4.2 Alignment

A common restriction of SIMD load and store instructions on modern processors is that access to data which is not aligned with vector registers is subject to a performance penalty compared to accessing aligned data.

Several works have addressed the issue of aligned access with vectorization. Eichenberger et al. and Wu et al. propose several heuristics which can deal with alignment issues while vectorizing, either statically [24] or at runtime [87]. Subsequently Fireman et al. present two algorithms which are optimal for special cases of the alignment problem [26]. However, all three assume that memory access, though it may be misaligned, is still consecutive.

## 2.5 Approximate Computing

Approximate computing is an emerging area of research [31]. The general idea is to design applications and hardware so that they can tolerate a loss of quality or accuracy in their results to improve performance or energy efficiency.

Some existing work has integrated approximate computing concepts into compilation systems. Petabricks is a language and compiler which supports variable accuracy algorithms [7]. Programmers provide multiple implementations of algorithms, and with the use of benchmarking and auto-tuning, the system selects the appropriate implementation for a new platform. Programmers can also provide accuracy constraints for the implementation of an algorithm using annotations, which the compiler can incorporate into the code generation process, producing faster but less accurate code. Green is another compiler system which supports approximate computing, which is targeted specifically at reducing the energy used by programs [9].

Chapter 4 introduces a method of generating low-level vectorized code to implement customized data storage formats, which are designed to represent reduced-accuracy results produced by approximate algorithms. The idea is to save space in memory (and reduce memory bandwidth) by using formats which have lower precision than natively supported types.

#### 2.5.1 Floating Point Programs with Reduced Accuracy

Exploiting reduced accuracy requirements in floating point computations to accelerate applications is the topic of several related works. Some, like Buttari et al. [16], choose to reduce precision in increments of the available native types on the platform. In the case of Buttari et al., their approach performs computationally expensive portions of numerical algorithms using single precision arithmetic, and less expensive portions using double precision arithmetic. They note that the choice of single precision arithmetic leads to speedups of up to 2x versus double precision for applications which are memory bound, due to the 2x reduction in the amount of data transferred through the memory bus.

This approach is also used by Rubio-Gonzalez et al. [71] who present an automated system which finds a compile-time instantiation of the types of floating point variables in the program which improves performance. Their approach is subject to accuracy constraints which are specified by the programmer via annotations in the source code. Like Buttari et al. [16] they consider only the available native machine types.

Lam et al. [41] also pursue this approach, by using binary instrumentation and translation to modify existing binaries and automatically find a satisfactory mixed-precision version of a program. Input programs are constrained to use double precision arithmetic only, and the system searches for program variables which can have their precision lowered without adversely affecting the computed results. Again, only natively supported types are considered for replacement.

#### 2.5.2 Customized Data Storage Formats

Programs which produce approximate results with reduced accuracy often do not require the full precision of native types to represent those results. In this situation, the use of full precision native formats can lead to inflated storage requirements and excess memory traffic. Using a specialized data storage format can reduce the amount of memory traffic created by the program, with associated gains in energy efficiency and overall runtime. Using vectorization to support specialized storage formats is particularly attractive. Vectorized execution provides a low-cost means of accelerating data reorganization and conversion by exploiting fine-grained data parallelism across multiple accesses. Vectorized implementations of specialized storage formats can make use of special vector reorganization instructions provided by modern processors, which are not available for scalar registers. In addition, vectorized execution is already the norm for many numerical applications.

### 2.5.3 Multibyte Floating Point

Jenkins et al. [33], propose to accelerate I/O performance of applications by reducing the resolution of the data. However, although the goal of that work is similar, there are several important differences with the approach we propose.

In terms of practical differences, an important distinction between the two pieces of work is that our approach parallelizes at the level of loop iterations, using vector memory access and vector reorganization to achieve a parallel speedup. Jenkins et al. evaluate their low-resolution scheme at extreme scale using thread-level parallelism via MPI, and using MPI to perform the data layout transformations. They note that a low-level vectorized approach appears to be promising future work given that data reorganization using MPI incurs significant overhead. In addition, the work of Jenkins et al. only deals with reads, whereas we propose an end-to-end approach which can deal with writes of reduced precision data in addition to reads.

Another important refinement over the work of Jenkins et al. is the topic of *rounding*, which is not addressed by that work. Jenkins et al. use simple truncation to obtain low-resolution data. This approach causes a measure of avoidable error which can be reduced significantly by performing correct rounding to select the nearest representable value in the target format for a given input value. In Chapter 4 we present a scheme for supporting custom floating point storage formats with correct rounding of data.

## 2.6 Summary and Directions for Improvement

Chapters 3 and 4 propose methods which generate SIMD code to efficiently implement memory access patterns which lack good hardware support – either by virtue of accessing data non-consecutively, or by accessing data stored in a format which does not correspond to native machine types.

In Chapter 3 we propose a generalization of the technique of Nuzman et al. [53] which removes the power-of-two constraint allowing vectorized code to be generated for a gathering or scattering operation with any compile-time constant stride.

Since difficult memory access patterns are often an impediment to vectorization [49], there appears to be significant value in a more general approach which can effectively vectorize a wider class of non-consecutive data access. Direct performance improvements aside, such an approach could act as an enabling technique for many of the vectorization tactics reviewed, allowing them to be applied to a wider range of programs by providing a way to generate SIMD code for more cases of non-consecutive memory access.

Previous work [48] has demonstrated some performance gains from transforming the layout of data in memory with scalar code just before the execution of vectorized code which accesses that data. However, being able to synthesize vectorized code to perform interleaved reads and writes directly in a vectorized loop or basic block means that instruction-level parallelism between data movement and computation can offset the overhead of memory access. This on-the-fly transformation of data layouts is the recommended mode of operation to achieve good performance using Intel's SIMD extensions [1].

In addition to our work on non-consecutive memory access, in Chapter 4, we propose a novel, low-level vectorized approach to supporting custom data formats. This is intended as a supporting technique for the area of approximate computing, reviewed in Section 2.5. We aim to reduce storage requirements and improve memory transfer times for programs with reduced-accuracy results.

# Chapter 3

# Vectorization of Static Affine Interleaving

Automatically exploiting short vector instructions sets is a critically important task for optimizing compilers. Vectorizing compilers identify program regions with fine-grained data parallelism and attempt to exploit this parallelism by transforming the program to use vectorized execution. Automatic vectorization is employed by many compilers, including those from the GNU Compiler Collection, LLVM, ICC, and more. Vectorized execution offers parallel speedups without the complexity of executing multiple independent instructions in parallel, and is therefore usually efficient in the use of hardware resources and energy.

However, automatic vectorization presents many problems in dependence analysis, code restructuring and data access patterns [8, 86]. A common data access pattern is where data items that are processed in different ways are interleaved together in memory. Unlike traditional vector processors which provided rich data access instructions for gather, scatter, and strided memory operations, modern short vector extensions typically provide very poor support for non-consecutive memory access. Short vector instructions work best on data that is contiguous in memory and operating on non-contiguous data requires the generation of additional instructions to perform *data layout transformation* packing and unpacking data elements between memory and vector registers. The need to reorganize data in vector registers has led to the inclusion of many specialized instructions for data layout transformation in vector instruction sets. For example, processors supporting Intel's SSE instruction set have the special shufps instruction, which selects even or odd indexed lanes (depending on the instruction mask) from two registers, and combines them in one register. ARM's NEON instruction set contains a similar v1d2 instruction, as does the Altivec instruction set (vperm). Such instructions typically include permutation of vector registers where the order of the items in the lanes of the register is changed, and combination of registers where a selection of lanes from different register are interleaved together. The presence of these instructions means that vectorization is well positioned as a supporting technique for other approaches which need to perform data layout transformations.

### 3.1 Modelling Arrays and Array Access

A dense array can be modelled as an indexed set of elements, where any two consecutive indices specify consecutive array elements. Similarly, an iterated access to such an array can be modelled as an indexed set, where any two consecutive indices specify array elements accessed by consecutive *loop iterations*. However, consecutive elements of the access are consecutive in the temporal sense, and are not required to be stored consecutively in the underlying array. When this is the case, we say that the access is non-contiguous. When multiple non-contiguous accesses share an underlying array, we say that the access pattern (i.e. the union of all accessed elements) is *interleaved*.

The relationship between *arrays* and *accesses* is captured by the *access function* for each access. The access function translates a loop iteration variable (which indexes elements of an access) so that it selects elements of an array. The access function can be any function of the loop iteration variable and potentially many more parameters. Many audio and video processing applications have access functions which are nonlinear and are implemented using lookup tables, and implementations of signal processing algorithms such as the fast Fourier transform often use exotic nonlinear access functions, such as bit-reversed ordering. Implementations of file systems, databases, and compression algorithms frequently use space-filling curves as access functions.

In this work we focus on the class of access functions which result in *Static Affine Interleaving*. This class encompasses all functions which are strictly affine transformations of the loop induction variable with respect to the arrays being accessed, where the values of all other parameters is statically known. Such functions have the following general form.

**Definition 1 (Access)** *We represent a strided access with iteration variable i as a function a of the form*

$$a(i) = b + u * (\texttt{stride} * i + \texttt{offset})$$

where *b* is the base address of the array, and *u* the unit size in bytes of an array element. The access is consecutive when |stride| is 1, and nonconsecutive otherwise. Note that the sign of the stride or offset may be negative.

For example, if the same array element is accessed in every loop iteration, stride may be instantiated to zero, and offset to the index of the accessed element in the underlying array. To visit every array element in order, stride may be instantiated to 1. To visit the elements of the array in reversed order, stride may be instantiated to -1, and offset to the length of the array, and so on.

Our approach to vectorizing such accesses follows a simple, general scheme: we cover the memory range accessed with non-overlapping vector loads or stores, and map individual accessed elements to loaded or stored lanes. The problem of vectorizing a strided access then becomes the problem of composing an ordered subset of loaded or stored lanes to or from a single vector register. In this chapter, we develop our approach by first showing how to create a vectorized code sequence in a simple, canonical form, and by application of successive optimizations, refine it into the final form which will be emitted. While our approach does not require aligned access, it may be desirable for performance reasons. Any implementation may apply a wide variety of possible techniques to ensure aligned access [24, 26]. One approach is to load extra lanes and discard those unused, treating the vector register file as a compilercontrolled cache [73]. However, this tactic has some corner cases: when the base address of the array is misaligned or the array does not contain enough data, an implementation using this tactic may have to apply array padding, or rely on masked vector loads or stores. Similarly, when loop trip counts are not a multiple of the vectorization factor (VF), extra iterations may need to be peeled and performed as scalar iterations.

#### 3.1.1 Notation and Presentation

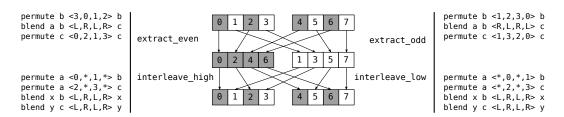

We specify our code generation in terms of a simple abstract instruction set. Similar to Wu et al., we use a representation with *virtual* vectors, and rely on a later native code generation phase to map these to the actual hardware [88].There are several motivations for this choice of instructions. Many architectures provide a large number of distinct specialized data reorganization instructions. Were we to state our code generation in terms of specialized instructions, it would restrict the applicability of our techniques to architectures with support for those instructions. The choice of a simple, generic form of permute and blend instructions ensures our approach is more widely applicable.

Second, the program transformations we propose in this chapter are quite succinct when expressed in terms of these simple instructions. Including many specialized data reorganization instructions would significantly complicate the presentation of our techniques.

Finally, it is important to note that on architectures which do have highly specialized data reorganization instructions, they do not go unused. Many multimedia architectures such as Intel SSE, AVX, AVX2, and ARM NEON provide such instructions in addition to generic instructions corresponding to those we include. However, many of the highly specialized native instructions for data reorganization can be expressed in terms of a short sequence of more generic permutes and blends. In this scenario, traditional tree-parsing instruction selection techniques [2] are very effective at selecting highly-specialized native instructions to cover the sequences of simplified operations which we generate. We detail our approach to native code generation in Section 3.4.6.

| Instruction | Arguments                                                                               |

|-------------|-----------------------------------------------------------------------------------------|

| load        | (Vector target, Pointer source)                                                         |

| store       | (Vector source, Pointer target)                                                         |

| permute     | $(Vector \ source, \ Vector \ mask, \ Vector \ target)$                                 |

| blend       | $({\tt Vector left}, \ {\tt Vector right}, \ {\tt Vector mask}, \ {\tt Vector target})$ |

Figure 3-1: The target intermediate representation for code generation.

We assume the following informal semantics for the instructions in Figure 3-1. load and store are packed vector load and store instructions. permute and blend are masked permutation and blending instructions. permute moves the *i*th lane of the source to the lane of the target given in the *i*th lane of the mask. blend selects the *i*th lane of the target from the left source if the *i*th mask lane is L, or from the right source if it is R.

#### Presentation

..

.

We write mask literals as a list of lane values enclosed in angled brackets. Vectors described by these masks have a common element size and type. Lanes containing the special \* mask element indicate a don't-care output in the lane. For example, the instruction permute a,  $\langle *, 0, *, 1 \rangle$ , b moves lanes 0 and 1 of vector a to lanes 1 and 3 of vector b, and leaves lanes 0 and 2 in an undefined state. In addition to the \* element, masks for the blend instruction may contain only the two special values L and R, indicating left and right source register, respectively. In graphical figures where data movement is indicated with arrows, an arrow with a solid line represents data movement using the permute instruction, and an arrow with a dashed line represents data movement using the blend instruction.

### 3.2 Technique

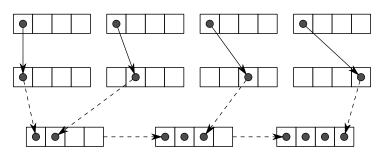

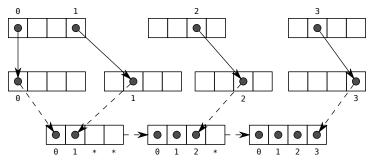

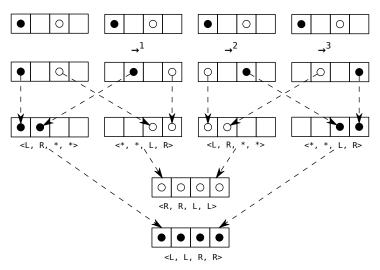

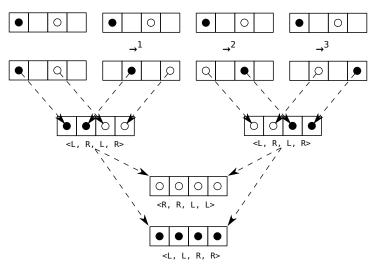

(a) Algorithm 1. Nonconsecutive read of the form a[4 \* i] with VF = 4. First we permute the load-mapped register set so that selected lanes will not collide under vertical composition with blend. We then blend the permuted registers together to form the packed vector corresponding to the access.

(b) Algorithm 2. Nonconsecutive write of the form a[4 \* i] with VF = 4. We expand the register to be stored into a register set which shadows the array region to be written. This store-mapped register set is then written over the shadowed array region with predicated writes, or using a read-modify-write sequence.

Figure 3-2: Vectorizing interleaved access using mapped register sets.

# 3.2.1 Enabling Interleaved Access: Automatically Vectorizing a Single Strided Access

We vectorize a nonconsecutive read by first mapping the memory range accessed end-to-end into vector registers (the load-mapped register set). By permuting and blending this register set together, we can extract any subset of up to VF lanes into a single packed vector register. We vectorize nonconsecutive writes similarly, by first mapping a store-mapped register set to the memory region being written. A non-consecutive write of data in a packed vector register is performed by expanding the register into a register set with items at the correct locations, and then combining this register set into the store-mapped register set using the blend instruction. It is important to stress that these registers are only logically mapped to memory — a mapped register will result in

the generation of a memory operation only if one or more lanes in the register are active.

Any vectorized strided access may touch elements in the range of (stride \* VF) consecutive memory locations in one memory operation. Since this memory region is mapped by registers of length VF elements, it follows that a maximum of stride mapped registers are required for a single vectorized access. Figures 3-2a and 3-2b show graphically the action of this simple canonical technique, and Algorithms 1 and 2 contain the logic required to generate the depicted instruction sequences.

Our approach has two phases: one phase permutes the mapped register set to eliminate lane collision when interleaving or deinterleaving, and the other phase takes a collision-free register set and combines registers using the blend instruction to form a packed result. To see why lane collision is a problem, consider Figure 3-2a: we cannot directly blend the initial mapped registers together, because multiple elements occupy the same lane in their respective registers, and collide when using the blend instruction.

```

ALGORITHM 1: Generate code to vectorize a read access (canonical)Input: A strided access a, load-mapped register set pOutput: s[VF - 1] contains VF packed consecutive elements of as \leftarrow allocate VF temporary registers;for i = 0 to VF - 1 domask \leftarrow \langle VF \times * \rangle;mask[i] \leftarrow ((stride * i) + offset) \mod VF;r \leftarrow p[((stride * i) + offset)/VF];generate: permute r, mask, s[i];endfor j = 1 to VF - 1 do| left \leftarrow j, right \leftarrow VF - j;mask \leftarrow \langle (left \times L) + (right \times R) \rangle;generate: blend s[j - 1], s[j], mask, s[j];

```

ALGORITHM 2: Generate code to vectorize a write access (canonical) Input: VF consecutive elements of a strided access a packed in register r **Output:** Store-mapped register set p contains the VF elements of a in store order pmask  $\leftarrow \langle VF \times * \rangle;$  $bmask \leftarrow \langle VF \times L \rangle;$  $pmasks \leftarrow stride copies of pmask;$  $\texttt{bmasks} \leftarrow \texttt{stride copies of bmask};$  $s \leftarrow$  allocate stride temporary registers; for i = 0 to VF - 1 do register  $\leftarrow (\texttt{stride} * i)/\texttt{VF};$ lane  $\leftarrow$  (stride \*i) mod VF; pmasks[register][lane]  $\leftarrow i$ ;  $bmasks[register][lane] \leftarrow R;$ generate: permute r, pmasks[register], s[register]; generate: blend p[register], s[register], bmasks[register], p[register]; end

# 3.2.2 Exploiting Spatial Locality: Grouping Multiple Interleaved Accesses

Multiple accesses to the same source or destination array can require overlapping vector loads or stores in a vectorized loop iteration if they share the same stride of access (shared-stride accesses). When this is the case, the accesses often exhibit spatial locality which can be exploited to reduce the number of memory operations in the vectorized program. Using the simple canonical approach from Section 3.2.1, we might generate loads and stores of the same data more than once. Similar to Nuzman et al. [53], we exploit this spatial locality by allowing multiple accesses to share mapped register sets when interleaving/deinterleaving, reducing the number of memory operations in the vectorized loop.

The degree of spatial locality present between any two shared-stride read or write accesses to the same array in vectorized loop iteration (i/VF) depends on the distance between accessed array elements in scalar loop iteration i, that is, the absolute difference between the offset of the two access functions. For any two shared-stride accesses with distinct offsets, three scenarios are possible.

- No locality When the distance between offsets is greater than or equal to (stride \* VF), the accesses do not overlap vector loads or stores in a vectorized loop iteration.

- (2) Partial locality When the distance is strictly less than (stride \* VF) and greater than or equal to stride, there is partial reuse — some elements of the first access will map to the same loaded or stored registers as elements of the second.

- (3) Full locality When the distance is strictly less than stride, there is full reuse in a vectorized loop iteration — all VF elements of each access map to the same set of vector loads or stores.

Note that our definition does not take into account temporal locality found along the backedge of the vectorized loop. Rather, we focus exclusively on exploiting spatial locality within VF iterations of the original loop.

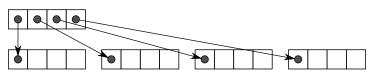

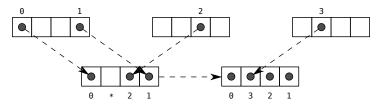

Consider the pair of shared-stride memory accesses a[4 \* i] and a[4 \* i + 1], from Figure 3-3a or 3-3b. This pair of accesses require the same vector memory operations in every vectorized loop iteration — the grouping exhibits *full locality* as we have defined it. However, when we include an access a[4 \* i + 5], it will require an extra memory operation in every vectorized loop iteration, because the underlying memory regions do not completely overlap (*partial locality*). Including another access, a[4 \* i + 7], that access would exhibit full locality with access a[4 \* i + 5], but only partial locality with accesses a[4 \* i ] and a[4 \* i + 1].

In order to minimize the number of vector memory operations for any number of shared-stride accesses, it is sufficient to consider only groups of maximal size, and load or store each resulting mapped register exactly once. However, minimizing the number of memory operations does not guarantee the generation of optimal vectorized code for a loop containing such accesses, which is a difficult optimization problem. Considerations include not only repeated memory operations, but also vector register spills and reloads due to register pressure and the scheduling of the instructions which perform the interleav-

(a) Algorithm 1. Two nonconsecutive reads of the form a[4 \* i] (dark dots) and a[4 \* i + 1] (light dots) with VF = 4, with shared spatial locality can be serviced from the same load-mapped register set using permute and blend sequences.

(b) Algorithm 2. Two nonconsecutive writes of the form a[4 \* i] (dark dots) and a[4 \* i + 1] (light dots) with VF = 4 are composed into a single store-mapped register set, reducing the number of stores required.

Figure 3-3: Sharing load-mapped/store-mapped register sets to exploit spatial locality.

ing/deinterleaving, which can exhibit significant instruction-level parallelism with the computation present in the loop. Barik et al. [11] demonstrate that good solutions to such problems require tight integration between vectorization, register allocation, and instruction scheduling during compilation.

We do not attempt to solve this optimization problem, but use the same simple, practical grouping heuristic for accesses with locality as Nuzman et al. [53] — group only those accesses which exhibit *full locality* as we have defined it. This approach yields significant speedup in practice, and does not require much engineering effort on the part of the compiler implementor.

In order to decide at compile time which shared-stride accesses can be serviced from a shared mapped register set, we introduce the analytic concept of an access group, which generalizes the similar concept of Nuzman et al. [53].

**Definition 2 (Access Group)** Accesses to the same array with the same direction (read or write) may be grouped by mapping each access offset to some interval [k, k + (stride - 1)], for  $k \in \mathbb{N}$ , where  $k \equiv 0 \mod stride$ . Each such interval, for any particular stride, defines a distinct access group at that stride. The size of an access group (written n) is bounded above by the shared stride of access of the group, and below by zero.

Let us assume we are considering two accesses  $a_0(i) = b_0 + u_0 * (\texttt{stride}_0 * i + \texttt{offset}_0)$  and  $a_1(i) = b_1 + u_1 * (\texttt{stride}_1 * i + \texttt{offset}_1)$ . These accesses can share the same load or store mapped register set iff

$$\begin{array}{l} \texttt{stride}_0 = \texttt{stride}_1\\ \\ u_0 = u_1\\ \lfloor (b_0 + u_0 * \texttt{offset}_0) / (u_0 * \texttt{stride}_0) \rfloor = \lfloor (b_1 + u_1 * \texttt{offset}_1) / (u_1 * \texttt{stride}_1) \rfloor \end{array}$$

This formulation groups accesses where stride of access and unit size are equal, and the accesses are relatively aligned within stride elements of the shared unit size of access. These criteria are sufficient to ensure that grouped accesses exhibit *full locality*. To vectorize such an access group, we repeatedly apply

Algorithm 1 or 2 but use only a single, shared mapped register set. Composing reads and writes into a shared mapped register set reduces the number of memory operations required for any group of n accesses. Since n is bounded above by the stride of access, and the number of mapped registers is exactly equal to the stride of access (Section 3.3.2), this sharing represents a reduction from worst-case  $O(n^2)$  memory operations considering individual accesses to O(n) operations considering the access group.

#### 3.2.3 Dealing with Store-Side Gaps

The work of Nuzman et al. [53] specifically excludes interleaved access patterns with store-side gaps. A *gap* is any unread or unwritten area of memory between elements of an interleaved access. Figure 3-3 displays two scenarios with gaps. In both examples in the figure, only two of the four lanes in each loaded or stored vector are used. While unused loaded lanes can simply be discarded, unused lanes in stores require the implementation to preserve the contents of memory in those lanes. As indicated in Figure 3-2, this may be achieved using predicated writes, or using a read-modify-write sequence. On both of our experimental platforms, predicated writes have very poor performance, while read-modify-write has excellent performance.

While predicated writes typically have the same semantics as the original scalar writes, any implementation using read-modify-write sequences may encounter race conditions due to the fact that a read-modify-write sequence modifies memory elements which were not modified by the scalar code. If the contents of memory corresponding to unused lanes changes between the read and write step of a sequence, data races and memory corruption can result. Broadly, there are three scenarios for such races: races between accesses in the same access group, races between different access groups, and thread-level races between multiple instances of the vectorized code operating on the same memory region.

For the class of (static-affine) accesses we consider, the technique of Chatarasi et al. [18] can be used to statically detect data races. The compiler may only

correctly parallelize statements where doing so would not create a data race. Our approach avoids the creation of races between accesses in the same access group by composing all the resulting memory reads or writes into a single mapped register set. Effectively, our technique coalesces vector memory operations in the compiler. Since our approach produces only one sequence of non-overlapping memory operations, we avoid introducing races between the accesses in any one access group.

To avoid inter-access group races, implementations which cannot use predicated writes may place read-modify-write sequences resulting from different access groups into atomic sections or use memory fences to ensure exclusive access to contested memory regions. The same approach may be used to avoid thread-level races. Where the hardware does not provide a way to ensure atomic execution of a group of instructions, or to create memory barriers, readmodify-write cannot always be used safely in a multithreaded context.

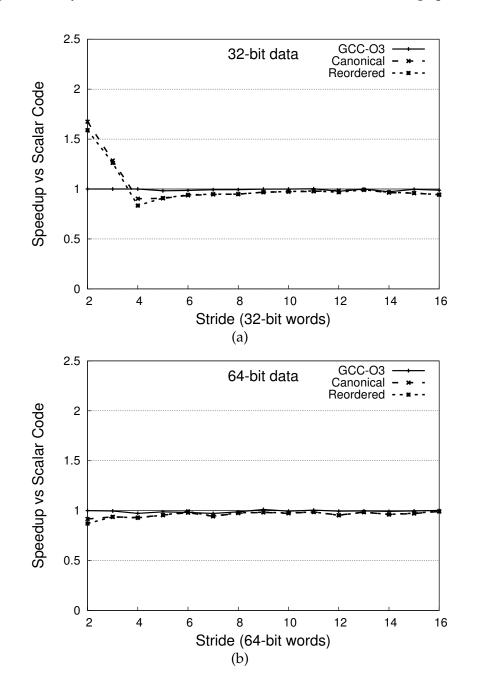

## 3.3 Optimization